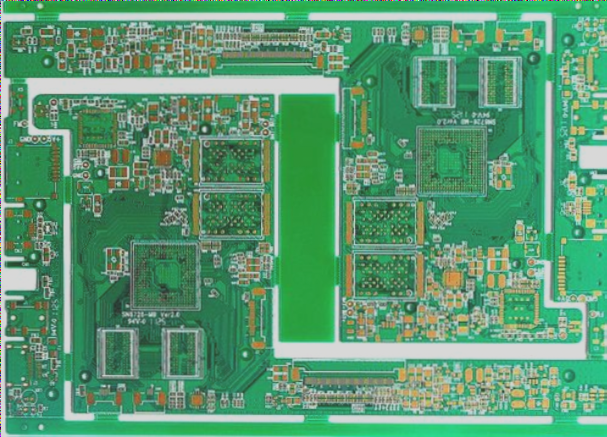

Decoupling Capacitor

When a chip is located far from its power source on a circuit board, it needs to draw power through the PCB traces. Placing a decoupling capacitor near the chip’s power pin is crucial to reduce high-frequency noise. Each VDD pin on a chip should have at least one decoupling capacitor, ideally positioned very close to the pin for effective noise reduction. Neglecting to place decoupling capacitors near power pins can greatly reduce their effectiveness. If your PCB design lacks proper placement of decoupling capacitors, it may indicate an incomplete design. If you’ve had issues with decoupling capacitors in your PCB design, consider seeking help from a different professional.

Balancing PCB Trace Lengths

For designs requiring precise timing alignment of multiple signals, it’s essential to ensure that PCB trace lengths are uniform. This is especially critical for routing high-speed clock signals to multiple chips or data and address buses connecting a microprocessor to RAM. Uniform trace lengths help maintain consistent signal delay, preserving signal edge relationships. To achieve this, refer to the schematic to identify signal lines needing precise timing alignment and verify trace lengths to confirm equalization has been achieved.

Keep in mind that vias in signal paths can introduce additional delay. If unavoidable, carefully examine all traces needing precise timing alignment and ensure they have an equal number of vias. Alternatively, consider using delay lines to compensate for delays caused by vias.