In terms of applications involving printed circuit boards, BGA packages are characterized by high success rates, low repair rates, and high reliability, making them increasingly prevalent. Board-level design heavily incorporates techniques for designing high-speed digital circuits. In such systems, noise interference generation is a critical factor, and high-frequency circuits also produce radiation and collisions. Faster edge rates lead to phenomena like ringing, reflections, and crosstalk. Failure to consider the intricacies of high-speed signal layout and wiring can result in malfunctioning circuit boards. Thus, the successful design of PCBs is a crucial aspect of DSP circuit design.

1. Transmission line effect

1.1 Signal Integrity

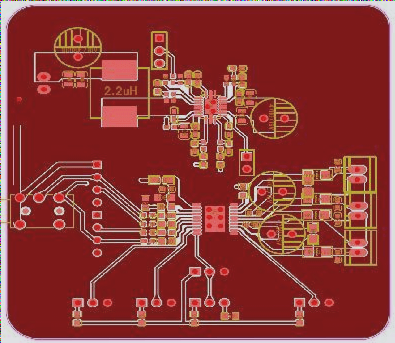

Signal integrity encompasses reflection, ringing, ground bounce, and crosstalk. PCB traces can be modeled as series and parallel structures of capacitors, resistors, and inductors (Figure 1). Typical series resistance values range from 0.25Ω to 4.55Ω, while parallel resistance is usually very high. The addition of parasitic elements such as resistance, capacitance, and inductance to actual PCB connections results in the characteristic impedance (Zo) of the connection. Mismatched impedance between the transmission line and the receiving end can cause signal reflections and oscillations.

The equivalent circuit of PCB traces:

Changes in routing geometry, improper wire termination, transmission through connectors, and power plane discontinuities can all induce reflections. Signal transitions during rising and falling edges can lead to overshoot and undershoot, generating glitches that exceed stable levels and potentially damaging devices. Improper inductance and capacitance in the line cause ringing and ringing of the signal, respectively, which can be mitigated through proper termination. Large current surges in circuits cause ground bounce, while transient currents through chip and board power planes induce power supply noise due to parasitic inductance and resistance between chip packages and power planes.

Crosstalk, a coupling issue between two signal lines, arises from mutual inductance and capacitance, introducing noise on the line. Capacitive coupling induces coupling current, whereas inductive coupling induces coupling voltage. PCB layer parameters, signal line spacing, driving and receiving end electrical characteristics, and termination methods all influence crosstalk to varying extents.

1.2 Solution: Some measures to solve common problems in PCB design are as follows:

The power plane should not restrict the direction of current flow. The return line can follow the impedance path close to the signal line, which forms current loops beneficial for high-speed systems. However, clutter on the power supply layer persists if the power distribution path is overlooked, leading to system-wide noise generation and errors. Thus, special filters are necessary, implemented through bypass capacitors.

Typically, a capacitor ranging from 1 to 10 µF is placed at the power input of the board. Additionally, capacitors ranging from 0.01 µF to 0.1 µF are positioned between the power and ground pins of each active device. These bypass capacitors act as filters: the larger capacitor (10 µF) at the power input filters low-frequency (60Hz) noise external to the board, while smaller capacitors between chips handle higher-frequency noise (typically 100MHz and above), including harmonic generation.

In designs combining analog and digital components, partitioning the PCB into separate analog and digital sections is crucial. Analog devices should be placed in the analog section, digital devices in the digital section, and the A/D converter bridging both areas. Segregated routing of analog and digital signals within their respective areas prevents digital return currents from interfering with analog signal grounds.

Bypassing and decoupling capacitors prevent energy transfer between circuits. Attention should be given to the power supply layer, signal trace layer, component placement, and internal power connections. Power and ground traces should be widened, with ground traces typically wider than power traces (e.g., power trace width: 1.2 mm to 2.5 mm; ground trace width: 0.07 mm wider).

Utilizing large-area copper layers for grounding and connecting unused areas of the PCB to ground further minimizes interference. Alternatively, multi-layer PCBs can dedicate individual layers to power and ground, optimizing noise reduction.

Each IC chip should be equipped with a 0.01 µF ceramic capacitor. For space-constrained PCBs, consider configuring 1 to 10 µF tantalum electrolytic capacitors for every 4 to 10 chips. These capacitors offer low impedance (500 kHz to 20 MHz) and minimal leakage current (< 0.5 µA).

Decoupling capacitors must be positioned close to integrated circuits, minimizing lead length and transient current loop area—especially critical for high-frequency bypass capacitors, which should ideally have no leads.

At system frequencies around 50 MHz, traditional methods can manage transmission line effects and signal integrity adequately. However, beyond 120 MHz, high-speed circuit design principles become essential for reliable PCB operation. Mastery of high-speed PCB circuit design is thus imperative for modern electronic system designers.

1. Transmission line effect

1.1 Signal Integrity

Signal integrity encompasses reflection, ringing, ground bounce, and crosstalk. PCB traces can be modeled as series and parallel structures of capacitors, resistors, and inductors (Figure 1). Typical series resistance values range from 0.25Ω to 4.55Ω, while parallel resistance is usually very high. The addition of parasitic elements such as resistance, capacitance, and inductance to actual PCB connections results in the characteristic impedance (Zo) of the connection. Mismatched impedance between the transmission line and the receiving end can cause signal reflections and oscillations.

The equivalent circuit of PCB traces:

Changes in routing geometry, improper wire termination, transmission through connectors, and power plane discontinuities can all induce reflections. Signal transitions during rising and falling edges can lead to overshoot and undershoot, generating glitches that exceed stable levels and potentially damaging devices. Improper inductance and capacitance in the line cause ringing and ringing of the signal, respectively, which can be mitigated through proper termination. Large current surges in circuits cause ground bounce, while transient currents through chip and board power planes induce power supply noise due to parasitic inductance and resistance between chip packages and power planes.

Crosstalk, a coupling issue between two signal lines, arises from mutual inductance and capacitance, introducing noise on the line. Capacitive coupling induces coupling current, whereas inductive coupling induces coupling voltage. PCB layer parameters, signal line spacing, driving and receiving end electrical characteristics, and termination methods all influence crosstalk to varying extents.

1.2 Solution: Some measures to solve common problems in PCB design are as follows:

The power plane should not restrict the direction of current flow. The return line can follow the impedance path close to the signal line, which forms current loops beneficial for high-speed systems. However, clutter on the power supply layer persists if the power distribution path is overlooked, leading to system-wide noise generation and errors. Thus, special filters are necessary, implemented through bypass capacitors.

Typically, a capacitor ranging from 1 to 10 µF is placed at the power input of the board. Additionally, capacitors ranging from 0.01 µF to 0.1 µF are positioned between the power and ground pins of each active device. These bypass capacitors act as filters: the larger capacitor (10 µF) at the power input filters low-frequency (60Hz) noise external to the board, while smaller capacitors between chips handle higher-frequency noise (typically 100MHz and above), including harmonic generation.

In designs combining analog and digital components, partitioning the PCB into separate analog and digital sections is crucial. Analog devices should be placed in the analog section, digital devices in the digital section, and the A/D converter bridging both areas. Segregated routing of analog and digital signals within their respective areas prevents digital return currents from interfering with analog signal grounds.

Bypassing and decoupling capacitors prevent energy transfer between circuits. Attention should be given to the power supply layer, signal trace layer, component placement, and internal power connections. Power and ground traces should be widened, with ground traces typically wider than power traces (e.g., power trace width: 1.2 mm to 2.5 mm; ground trace width: 0.07 mm wider).

Utilizing large-area copper layers for grounding and connecting unused areas of the PCB to ground further minimizes interference. Alternatively, multi-layer PCBs can dedicate individual layers to power and ground, optimizing noise reduction.

Each IC chip should be equipped with a 0.01 µF ceramic capacitor. For space-constrained PCBs, consider configuring 1 to 10 µF tantalum electrolytic capacitors for every 4 to 10 chips. These capacitors offer low impedance (500 kHz to 20 MHz) and minimal leakage current (< 0.5 µA).

Decoupling capacitors must be positioned close to integrated circuits, minimizing lead length and transient current loop area—especially critical for high-frequency bypass capacitors, which should ideally have no leads.

At system frequencies around 50 MHz, traditional methods can manage transmission line effects and signal integrity adequately. However, beyond 120 MHz, high-speed circuit design principles become essential for reliable PCB operation. Mastery of high-speed PCB circuit design is thus imperative for modern electronic system designers.