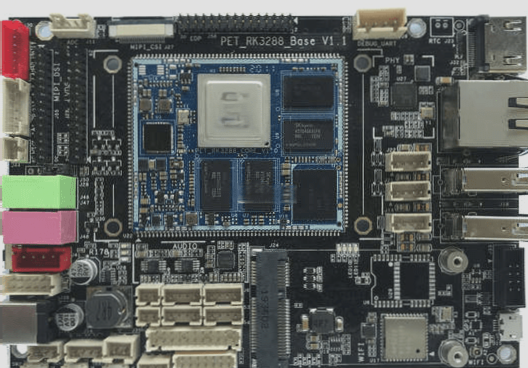

On the PCB board, for the analysis of simultaneous switching noise (SSN) in FPGAs, today’s CMOS technology enables a single FPGA device to have multiple I/O interfaces. In recent years, low power consumption has become the mainstream concept for high-speed I/O interfaces. One effective method to reduce power consumption is to decrease the voltage, but this also results in a smaller noise margin allowed by the I/O interface. Therefore, it is crucial for FPGA users to accurately measure and quantify system-level SSN in the context of chips, packages, and PCBs.

This article provides a comprehensive introduction to SSN, with a specific focus on SSN caused by FPGA output buffering, which is commonly referred to as synchronous switching output noise (SSO). It distinguishes SSO from SSN caused by input buffering. The paper discusses the various factors that contribute to system-level SSO and proposes a hierarchical system-level SSO modeling approach. Moreover, it explains how to correlate the SSO model with frequency and time domain measurements. In addition, the article presents several PCB board design techniques that can effectively reduce SSO.

The formation mechanism of system-level SSO

A PCB board with an FPGA is a complex system that can be divided into a wafer section containing active circuits, a package section with embedded passives that support traces, and a circuit board section that provides connections for the FPGA to the outside world. In such systems, it is difficult to understand the noise characteristics inside the chip. Therefore, it is valuable to quantify the SSO at the near and far ends of the PCB traces connected to the FPGA. There are two main factors that cause SSO: the impedance of the power distribution network (PDN) and the mutual inductive coupling between switch I/Os.

From a system perspective, a PDN contains wafer-level, package-level, and board-level components that collectively power CMOS circuits. When a certain number of CMOS output driver circuits are turned on at the same time, a large current will flow into the inductive circuit elements of the PDN instantaneously, resulting in a delta-I voltage drop. Interconnect structures create parasitic inductances, such as power solder balls on ball grid array packages and power vias in PCB board. This rapidly changing current also excites radial electromagnetic waves between the power/ground plane pair, which bounce off the plane edges of the PCB board, resonating between the power/ground planes, causing voltage fluctuations. Another important cause of SSO is mutual inductive coupling, especially around the edge of the chip package/PCB board. The solder balls on the chip BGA package and the vias on the PCB belong to the tightly coupled multi-conductor structure. Each I/O solder ball and its corresponding PCB board via form a closed loop with the ground solder ball and ground via near it. When the state of multiple I/O ports changes simultaneously, transient I/O currents flow through these signal loops. This transient I/O current in turn creates a time-varying magnetic field that intrudes into adjacent signal loops and induces voltage noise.

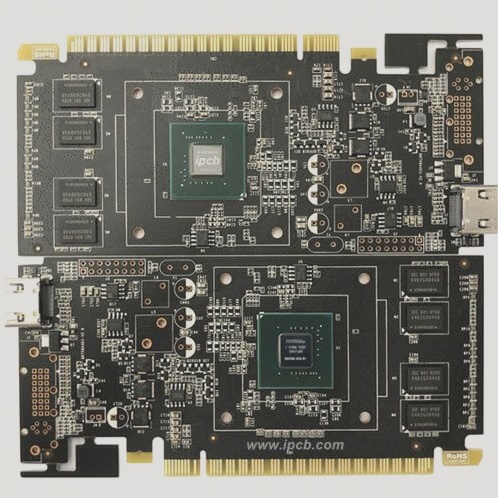

An SSO model should be able to reflect the basic formation mechanism of SSO. Figure 1 shows a layered model for predicting SSO in a PCB. On the wafer, what is needed is an output buffer model that provides current distribution on power and signal lines with limited complexity. In encapsulation, for the sake of simplicity, the PDN model and the signal coupling model can be obtained separately by using modeling tools, but the interaction between the PDN and the signal coupling model should be carefully considered. These two models act as a bridge, connecting the output buffer model on the bump side of the chip package and the PCB board-level model on the solder ball side. The PDN model of a PCB usually includes power/ground planes and bulk/decoupling capacitors on them, while the signal coupling model of a PCB includes an array of tightly coupled vias and loosely coupled signal traces on different signal layers. The interaction effect of these two PCB board-level models occurs in the PCB board via array, and it is from here that the inductive crosstalk brings noise into the PDN model, and the delta-I noise in turn degrades the I/O signal quality. This hierarchical modeling approach reasonably maintains simulation accuracy while also improving computational efficiency for such complex systems.

In the following, for the printed circuit boards equipped with FPGA, two basic design methods to reduce SSO based on the SSO generation mechanism are introduced.

1. Design method to reduce inductive coupling

The simulation results show that the inductive coupling at the chip package/PCB interface is the culprit that causes high frequency spikes in the SSO waveform. A signal loop with a size of t × d consists of a signal via and a ground via close to it. The size of this loop indicates the strength of the inductive coupling. The larger the area of the I/O disturbing loop, the easier it is for the generated magnetic field to intrude into the adjacent disturbed loop. The larger the area of the disturbed I/O signal loop, the easier it is to be disturbed by other I/O loops. Therefore, in order to reduce the crosstalk and parameter t, attention should be paid to the use of thinner PCB boards in the design, and the key I/Os on the PCB board should be drawn from the shallower signal layer. At the same time, designers can reduce crosstalk by shortening the distance between I/O vias and ground vias. The designer specially connected a pair of I/O pads to the ground plane and the VCCIO plane to reduce the signal loop area corresponding to the disturbed pins and the disturbed pins. Experimental tests show that the ground bounce on AF30 in Bank1 has been reduced by 17% compared to G30 in Bank 2, and the power sag has also been reduced by 13%. Simulation results also verify this improvement. Since the presence of programmable ground pins shortens the distance d between the disturbing loop and the disturbed loop, the reduction in SSO is expected, as shown in Figure 2. However, the improvement is limited because the signal loop area in the chip package cannot be reduced.

2. Reduce PDN impedance through reasonable design

The impedance between VCCIO and ground pins at the interface on the PCB is an important criterion for evaluating the PDN performance of an FPGA chip. This input impedance can be reduced by employing effective decoupling strategies and using thinner power/ground plane pairs. However, an effective method is to shorten the length of the power vias that connect the VCCIO solder balls to the VCCIO plane. Also, shortening the power via also reduces the loop it forms with the adjacent ground via, making the loop less susceptible to disturbing I/O loop state changes. Therefore, the design should arrange the VCCIO plane closer to the top layer of the PCB.

This article provides a comprehensive analysis of simultaneous switching noise simulations on a PCB board with an FPGA. The analysis results show that the crosstalk on the interface between the package and the PCB and the PDN impedance distribution on the package and the PCB are two important causes of SSO. Correlation models can be used to help PCB board designers reduce SSO and achieve better PCB board design. Several methods to reduce SSO are also introduced in the paper. Among them, rational allocation of signal layers and full use of programmable ground/power pins can help reduce inductive crosstalk at the PCB board level, and arranging VCCIO in a shallow position in the PCB board stackup can also reduce PDN impedance.

This article provides a comprehensive introduction to SSN, with a specific focus on SSN caused by FPGA output buffering, which is commonly referred to as synchronous switching output noise (SSO). It distinguishes SSO from SSN caused by input buffering. The paper discusses the various factors that contribute to system-level SSO and proposes a hierarchical system-level SSO modeling approach. Moreover, it explains how to correlate the SSO model with frequency and time domain measurements. In addition, the article presents several PCB board design techniques that can effectively reduce SSO.

The formation mechanism of system-level SSO

A PCB board with an FPGA is a complex system that can be divided into a wafer section containing active circuits, a package section with embedded passives that support traces, and a circuit board section that provides connections for the FPGA to the outside world. In such systems, it is difficult to understand the noise characteristics inside the chip. Therefore, it is valuable to quantify the SSO at the near and far ends of the PCB traces connected to the FPGA. There are two main factors that cause SSO: the impedance of the power distribution network (PDN) and the mutual inductive coupling between switch I/Os.

From a system perspective, a PDN contains wafer-level, package-level, and board-level components that collectively power CMOS circuits. When a certain number of CMOS output driver circuits are turned on at the same time, a large current will flow into the inductive circuit elements of the PDN instantaneously, resulting in a delta-I voltage drop. Interconnect structures create parasitic inductances, such as power solder balls on ball grid array packages and power vias in PCB board. This rapidly changing current also excites radial electromagnetic waves between the power/ground plane pair, which bounce off the plane edges of the PCB board, resonating between the power/ground planes, causing voltage fluctuations. Another important cause of SSO is mutual inductive coupling, especially around the edge of the chip package/PCB board. The solder balls on the chip BGA package and the vias on the PCB belong to the tightly coupled multi-conductor structure. Each I/O solder ball and its corresponding PCB board via form a closed loop with the ground solder ball and ground via near it. When the state of multiple I/O ports changes simultaneously, transient I/O currents flow through these signal loops. This transient I/O current in turn creates a time-varying magnetic field that intrudes into adjacent signal loops and induces voltage noise.

An SSO model should be able to reflect the basic formation mechanism of SSO. Figure 1 shows a layered model for predicting SSO in a PCB. On the wafer, what is needed is an output buffer model that provides current distribution on power and signal lines with limited complexity. In encapsulation, for the sake of simplicity, the PDN model and the signal coupling model can be obtained separately by using modeling tools, but the interaction between the PDN and the signal coupling model should be carefully considered. These two models act as a bridge, connecting the output buffer model on the bump side of the chip package and the PCB board-level model on the solder ball side. The PDN model of a PCB usually includes power/ground planes and bulk/decoupling capacitors on them, while the signal coupling model of a PCB includes an array of tightly coupled vias and loosely coupled signal traces on different signal layers. The interaction effect of these two PCB board-level models occurs in the PCB board via array, and it is from here that the inductive crosstalk brings noise into the PDN model, and the delta-I noise in turn degrades the I/O signal quality. This hierarchical modeling approach reasonably maintains simulation accuracy while also improving computational efficiency for such complex systems.

In the following, for the printed circuit boards equipped with FPGA, two basic design methods to reduce SSO based on the SSO generation mechanism are introduced.

1. Design method to reduce inductive coupling

The simulation results show that the inductive coupling at the chip package/PCB interface is the culprit that causes high frequency spikes in the SSO waveform. A signal loop with a size of t × d consists of a signal via and a ground via close to it. The size of this loop indicates the strength of the inductive coupling. The larger the area of the I/O disturbing loop, the easier it is for the generated magnetic field to intrude into the adjacent disturbed loop. The larger the area of the disturbed I/O signal loop, the easier it is to be disturbed by other I/O loops. Therefore, in order to reduce the crosstalk and parameter t, attention should be paid to the use of thinner PCB boards in the design, and the key I/Os on the PCB board should be drawn from the shallower signal layer. At the same time, designers can reduce crosstalk by shortening the distance between I/O vias and ground vias. The designer specially connected a pair of I/O pads to the ground plane and the VCCIO plane to reduce the signal loop area corresponding to the disturbed pins and the disturbed pins. Experimental tests show that the ground bounce on AF30 in Bank1 has been reduced by 17% compared to G30 in Bank 2, and the power sag has also been reduced by 13%. Simulation results also verify this improvement. Since the presence of programmable ground pins shortens the distance d between the disturbing loop and the disturbed loop, the reduction in SSO is expected, as shown in Figure 2. However, the improvement is limited because the signal loop area in the chip package cannot be reduced.

2. Reduce PDN impedance through reasonable design

The impedance between VCCIO and ground pins at the interface on the PCB is an important criterion for evaluating the PDN performance of an FPGA chip. This input impedance can be reduced by employing effective decoupling strategies and using thinner power/ground plane pairs. However, an effective method is to shorten the length of the power vias that connect the VCCIO solder balls to the VCCIO plane. Also, shortening the power via also reduces the loop it forms with the adjacent ground via, making the loop less susceptible to disturbing I/O loop state changes. Therefore, the design should arrange the VCCIO plane closer to the top layer of the PCB.

This article provides a comprehensive analysis of simultaneous switching noise simulations on a PCB board with an FPGA. The analysis results show that the crosstalk on the interface between the package and the PCB and the PDN impedance distribution on the package and the PCB are two important causes of SSO. Correlation models can be used to help PCB board designers reduce SSO and achieve better PCB board design. Several methods to reduce SSO are also introduced in the paper. Among them, rational allocation of signal layers and full use of programmable ground/power pins can help reduce inductive crosstalk at the PCB board level, and arranging VCCIO in a shallow position in the PCB board stackup can also reduce PDN impedance.