Effective Anti-ESD Measures in PCB Design

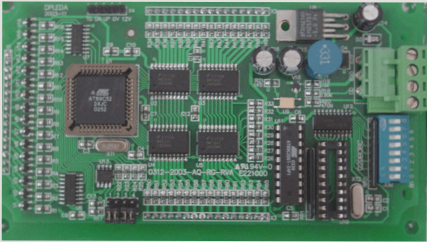

In the realm of printed circuit board (PCB) design, implementing effective anti-electrostatic discharge (ESD) measures is crucial to safeguard precision semiconductor chips from potential damage caused by static electricity. These damages may include penetration of thin insulating layers, short-circuiting of PN junctions, and melting of bonding wires within active devices. To combat these issues, various technical measures must be put in place.

One effective strategy is to focus on strategic layering, proper layout, and meticulous installation techniques during the PCB design process. By making adjustments to the PCB layout, ESD incidents can be effectively prevented. Here are some key considerations:

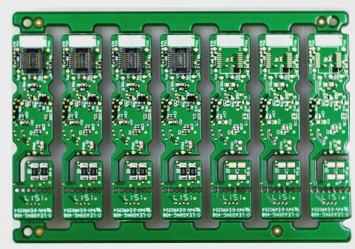

- Utilize Multi-layer PCBs: Opt for multi-layer PCBs over double-sided ones to take advantage of ground and power planes, closely spaced signal lines, and ground lines, which help reduce common-mode impedance and inductive coupling.

- Optimize Signal Layer Placement: Position signal layers in close proximity to power or ground layers, especially in high-density PCBs with components on both surfaces.

- Implement Power and Ground Grids: Use densely woven power and ground grids, ensuring a tight connection between power and ground lines.

- Design Compact Circuits: Keep circuits compact to minimize exposed connectors and consider routing power cables through the card center.

- Grounding Strategies: Employ wide chassis grounds beneath connectors prone to ESD hits and maintain proper isolation and ground connections.

- Ring Ground Design: Incorporate a ring ground around the circuit to enhance grounding effectiveness.

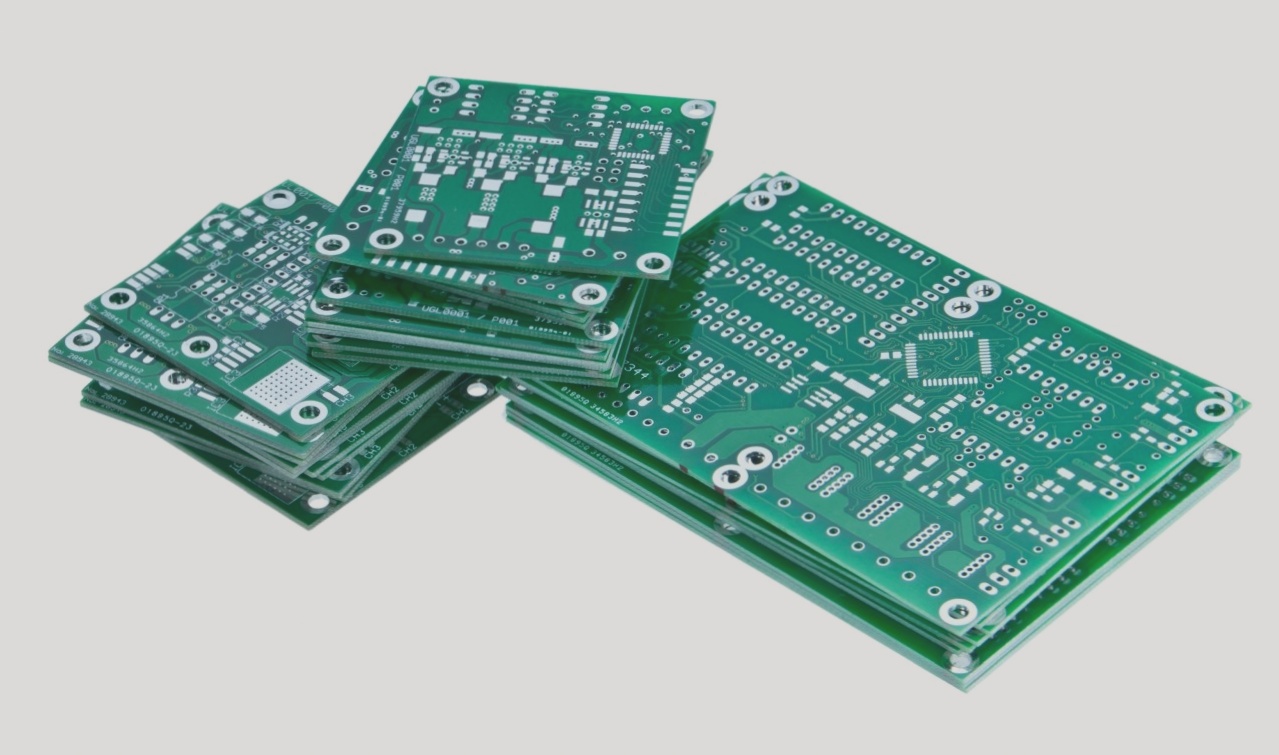

- Include ESD Protection Components: Integrate series resistors, magnetic beads, transient protectors, and filter capacitors to mitigate ESD effects.

- Focus on Optimized Routing: Keep signal lines short and direct, avoiding parallel routing of protected and unprotected lines.

- Consider Installation Practices: Insert PCBs into chassis to minimize signal line interference.

By adhering to these guidelines and incorporating anti-ESD measures into PCB design, the risks associated with electrostatic discharge can be significantly reduced, ensuring the reliability and longevity of electronic equipment.