### The Impact of Vias in High-Speed PCBs

In high-speed, multi-layer PCBs, signal transmission between different layers of interconnection lines relies on vias. For frequencies below 1 GHz, vias generally provide an effective connection, and their parasitic capacitance and inductance are negligible.

However, when the frequency exceeds 1 GHz, the parasitic effects of the via become significant and can impact signal integrity. In this case, vias introduce discontinuities in the transmission path, resulting in impedance mismatches that can lead to signal reflections, delays, attenuation, and other integrity issues.

When a signal is routed to another layer via a via hole, the reference layer for the signal also acts as the return path for the via signal. The return current then flows between reference layers via capacitive coupling, potentially causing issues like ground bounce.

### Types of Vias

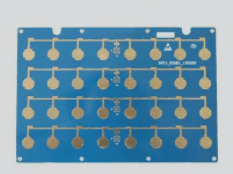

Vias are generally categorized into three types: through holes, blind holes, and buried holes.

– **Blind Hole**: Located on the top and bottom surfaces of the PCB, blind holes have a defined depth and are used to connect surface traces to the internal circuits below. The hole’s depth and diameter typically have a specific ratio limit.

– **Buried Hole**: A buried via connects layers within the PCB but does not extend to the surface. These vias are used for internal layer interconnections.

– **Through Hole**: A through hole passes through the entire PCB and can be used for inter-layer connections or as mounting holes for components. Through holes are relatively easier and more cost-effective to manufacture, making them the most commonly used via type in PCBs.

### Parasitic Capacitance of Vias

Vias inherently have parasitic capacitance to ground. If the diameter of the isolation hole in the ground layer of the via is (D_2), the diameter of the via pad is (D_1), the PCB thickness is (T), and the dielectric constant of the board substrate is (varepsilon), the parasitic capacitance of the via can be approximated as:

[

C = frac{1.41 varepsilon T D_1}{D_2 – D_1}

]

The primary effect of the via’s parasitic capacitance on the circuit is to slow down the rise time of the signal, thereby reducing the circuit’s speed. The smaller the capacitance, the less noticeable the effect.

### Parasitic Inductance of Vias

Here is the revised version of the article with slight adjustments to the phrasing while maintaining the original meaning and technical accuracy:

—

1. **Parasitic Inductance of the Via**

The via itself introduces parasitic inductance. In high-speed digital circuit design, the impact of the parasitic inductance from the via is often more detrimental than the effect of parasitic capacitance. The parasitic series inductance of the via can degrade the performance of bypass capacitors and diminish the filtering capability of the overall power system. If ( L ) represents the via inductance, ( h ) is the via length, and ( d ) is the diameter of the center hole, the parasitic inductance of the via can be approximated as:

[ L = 5.08h left[ lnleft( frac{4h}{d} right) – 1 right] ]

From this formula, it is evident that the diameter of the via has a relatively minor effect on the inductance, while the length of the via has the most significant impact on the inductance.

2. **Via Design in High-Speed PCBs**

In high-speed PCB design, vias, though seemingly simple, can introduce substantial negative effects on circuit performance. To mitigate the adverse impact of parasitic effects from vias, the following design practices are recommended:

(1) **Select an appropriate via size**. For multi-layer, general-density PCB designs, typical via dimensions are 0.25mm (drill hole) / 0.51mm (pad) / 0.91mm (POWER isolation area). For high-density PCBs, vias with sizes of 0.20mm (drill hole) / 0.46mm (pad) / 0.86mm (isolation area) may be used. Non-through vias can also be considered. For power or ground vias, larger sizes may be beneficial to reduce impedance.

(2) **Maximize the POWER isolation area**. Considering the via density on the PCB, a typical rule of thumb is ( D1 = D2 + 0.41 ).

(3) **Minimize the use of vias in signal traces**. This means reducing the number of vias as much as possible, as unnecessary vias can introduce additional parasitic effects.

(4) **Use a thinner PCB**. A thinner PCB helps to reduce the parasitic inductance and capacitance associated with vias.

(5) **Place power and ground pins close to the vias**. The shorter the lead between the vias and the power or ground pins, the better, as this reduces the inductance. Additionally, power and ground traces should be as wide as possible to minimize impedance.

(6) **Add grounding vias near signal vias**. This creates a short-loop path for signals, which helps maintain signal integrity.

3. **Via Length and Its Impact on Inductance**

The length of the via is a critical factor in determining its inductance. For vias connecting the top and bottom layers, the via length is typically equal to the thickness of the PCB. As the number of PCB layers increases, the thickness of the PCB can exceed 5mm. However, in high-speed PCB designs, to minimize the issues caused by vias, the via length is usually kept under 2.0mm. For vias longer than 2.0mm, increasing the via diameter can improve impedance continuity to some extent. For vias with a length of 1.0mm or less, the optimal via hole diameter is typically between 0.20mm and 0.30mm.

If your have any questions about PCB ,please contact me info@wellcircuits.com