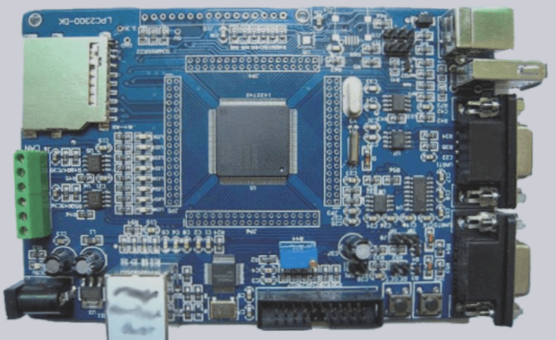

The Evolution of PCB Testing and Debugging

As circuit boards become more complex, traditional testing methods with oscilloscopes and logic analyzers are proving to be inadequate. The emergence of EDA simulators and waveform viewers has revolutionized the debugging process by utilizing thousands of time domains to monitor signals, expanding the scope of debugging activities.

The Role of Board-Level Simulation Technology

Board-level simulation tools play a crucial role in accelerating the debugging process for PCB designers, enabling them to identify and address defects early on, ultimately saving time and money in the circuit board design and production cycle.

Key Steps in Board-Level Simulation

- Developing a Test Plan: Creating a comprehensive test plan is the first step in board-level simulation, focusing on individual interface testing and overall functional testing of the circuit board.

- Establishing a Simulation Environment: Setting up a simulation environment with checkers, monitors, netlists, models, and a directory structure is essential for processing and analyzing input and output signals.

Advantages of Simulation Tools

- Efficient Error Logging: Simulation tools automatically log errors and defects, streamlining the debugging process.

- Time-Saving Analysis: Writing comparison scripts and utilizing flags to indicate fault conditions during simulation significantly reduces analysis time.

- Component Modeling: Using HDL models for components allows for flexible timing adjustments to meet specific requirements.

Conclusion

Board-level simulation technology is a game-changer in the world of PCB design and production, offering advanced capabilities that enhance efficiency and accuracy in testing and debugging processes.

PCB Design and Simulation Best Practices

PCB designers need to establish a well-organized directory structure to manage input/output signals effectively during the simulation process. The directory should categorize various environment files such as cs, local development models, monitors/inspectors, scripts, board-level netlists, log files, and dump files to facilitate easy tracking and management.

Simulating Functional Blocks

When utilizing the framer/deframer as a simulated functional block, focus on testing the excitation signal from the PCI side and verifying the output on the T1/E1 digital line side. Reverse the process to ensure proper functionality.

Test Scenarios

- Frames with varied data content

- Frame delays

- Super frames or extended super frames with different parameter settings

- Frames with CRC errors

Verification of Functional Blocks

Other functional blocks should undergo similar simulation processes to validate results. Common defects during testing may include duplicate network names causing short circuits, system integration issues, and unsupported data formats between interfaces. This phase is crucial for data channel simulation on the circuit board.

Simulation Strategies

Consider the following tips for board-level simulation:

- Utilize back-labeling files for programmable PCB components to manage input and output signal timing.

- Ensure all power supply network descriptions in the netlist are accurate and complete.

- Attention to components not directly linked to the circuit board is essential.

Limitations of Functional Simulation

While functional simulation offers many benefits, it has limitations that may impact the accuracy of PCB behavior replication:

- Lack of specific power network identifications in HDL.

- Inability to simulate analog interfaces.

- Potential oversight of drive capability issues.

- Memory tests requiring large dump files and extended execution times.