Working with Multiple SPI ICs on a Single Bus

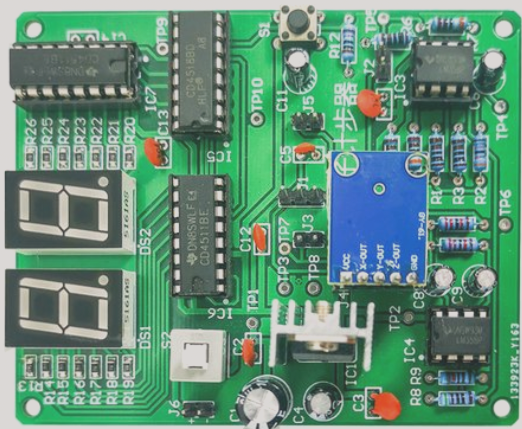

When dealing with multiple SPI ICs on a single bus, careful routing is crucial. In this scenario, the bus spans 310 mm, with signals inserted in the middle and a maximum SPI clock speed of <10MHz. The board is two-sided with a ground flood fill in between.

Two main concerns arise:

- Routing the clock line over other lines may cause signal integrity issues. It’s essential to assess the impact of this configuration.

- Considering the bus length of 310mm, ensuring signal integrity over such a distance is vital. Divide the length by 2 (155mm on each side) to manage signal propagation effectively.

While a full layout cannot be shared due to project constraints, addressing these concerns will help optimize the performance of your SPI ICs on the bus.

For more insights and solutions to optimize your PCB design, stay tuned for the latest updates in the field of PCB technology.

Thank you for your attention.