1. Like most effective high-density analog layout and routing strategies, the design must fulfill the routing requirements, and a balance between layout and routing must be achieved.

2. For the analog section of a mixed-signal PCB paired with a local CPU core operating at 2V, employing the “layout before wiring” approach is not advisable.

3. For the OC48 card, the DSP analog circuitry, including the analog reference voltage and the analog power supply bypass capacitor, should be wired interactively first.

4. Once the wiring is complete, ensure that the entire DSP along with its analog components and connections is positioned close enough to the optical transceiver to guarantee minimal wiring length, with minimal bends and vias for the high-speed analog differential signals to the DSP.

5. Maintaining symmetry in the differential layout and routing will help mitigate the effects of common mode noise. However, predicting the optimal layout before routing can be challenging.

6. Consult the chip distributor for PCB layout design guidelines. Before proceeding with the design based on these guidelines, it is essential to engage thoroughly with the distributor’s application engineer.

7. Many chip distributors impose strict time limits on providing quality layout recommendations. Often, the solutions they offer are tailored for “first-level customers” who utilize the device.

8. In the realm of signal integrity (SI) design, ensuring the signal integrity of new devices is particularly crucial. Following the distributor’s fundamental guidelines and considering the specific needs of each power and ground pin in the package will allow you to begin laying out and routing the OC48 card with the integrated DSP and microprocessor.

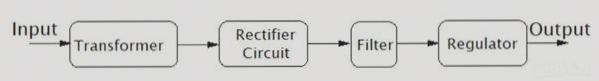

9. After finalizing the location and wiring of the high-frequency analog components, the remaining digital circuits can be positioned according to the grouping method illustrated in the block diagram.

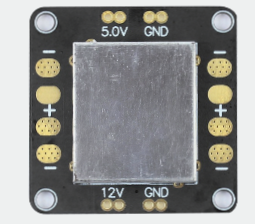

10. It is vital to carefully design the following circuits: the placement of the PLL power filter circuit in the CPU, which is highly sensitive to analog signals; the voltage regulator for the local CPU core; and the reference voltage circuit for the “digital” microprocessor.

1. The electrical and manufacturing guidelines for digital wiring can be effectively implemented in the current design phase. The previously mentioned design considerations for signal integrity in high-speed digital buses and clock signals highlight specific wiring topology requirements for the processor bus, balanced T-lines, and timing delay matching of certain clock signal traces. Interestingly, some experts have proposed an updated recommendation: to add more termination resistors.

2. During the problem-solving process, it is natural to make adjustments at the layout stage. However, before initiating the PCB layout, a critical step is to verify the timing of the digital components in accordance with the layout plan. At this stage, a thorough DFM/DFT layout review of the board will help ensure that the design meets customer requirements.

3. Digital wiring for the OC48 card should begin with the SMD escape patterns for the power lines of digital devices and the digital section of the mixed-signal DSP. Use the shortest and widest printed traces permissible by the assembly process. For high-frequency devices, the printed power lines behave like small inductors, which can exacerbate power supply noise and lead to unwanted coupling between analog and digital circuits. The longer the power trace, the higher the inductance.

4. Employing digital bypass capacitors can optimize the layout and routing scheme. Essentially, fine-tune the placement of the bypass capacitors as necessary to facilitate installation and distribute them around both the digital section and the digital portion of the mixed-signal device. Utilize the same “shortest and widest trace” approach for routing the bypass capacitors.

5. When a power supply branch traverses a continuous plane (such as the 3.3V power plane on the OC48 interface card), the power supply pin and the bypass capacitor do not need to share the same outlet diagram, enabling the lowest possible inductance and ESR bypass. On mixed-signal PCBs like the OC48 interface card, pay special attention to the wiring of the power supply branch. It’s essential to place additional bypass capacitors in a matrix configuration throughout the card, even near passive components.

6. Once the power outlet diagram is finalized, you can proceed with automatic routing. The ATE test contacts on the OC48 card should be defined during the logic design phase. Ensure that ATE probes connect to 100% of the nodes. To facilitate ATE testing with the smallest probe size of 0.070 inches, the placement of breakout vias must be carefully reserved to prevent interruption of the power plane by via antipads.

7. If employing a split solution for power and ground planes, select a layer bias on the adjacent wiring layer parallel to the opening. Define restricted wiring areas on the adjacent layer based on the perimeter of the opening to prevent undesired wiring. If the traces must cross through the open area to another layer, ensure that the adjacent layer is a continuous ground plane. This approach will minimize the reflection path. While it’s beneficial for some digital signals to have bypass capacitors across the open power plane, bridging between digital and analog power planes is discouraged due to potential noise coupling through the bypass capacitors.

8. In mixed-signal PCB design, several cutting-edge automatic routing applications can effectively handle high-density multi-layer digital circuits. In the initial wiring phase, utilize 0.050-inch large via spacing at the SMD exit and consider the package type employed. In subsequent wiring stages, allow vias to be placed closer together to achieve the highest layout efficiency with the fewest vias. Given that the OC48 processor bus employs an enhanced star topology, it takes precedence during automatic routing.

If you have any PCB manufacturing needs, please do not hesitate to contact me.Contact me

2. For the analog section of a mixed-signal PCB paired with a local CPU core operating at 2V, employing the “layout before wiring” approach is not advisable.

3. For the OC48 card, the DSP analog circuitry, including the analog reference voltage and the analog power supply bypass capacitor, should be wired interactively first.

4. Once the wiring is complete, ensure that the entire DSP along with its analog components and connections is positioned close enough to the optical transceiver to guarantee minimal wiring length, with minimal bends and vias for the high-speed analog differential signals to the DSP.

5. Maintaining symmetry in the differential layout and routing will help mitigate the effects of common mode noise. However, predicting the optimal layout before routing can be challenging.

6. Consult the chip distributor for PCB layout design guidelines. Before proceeding with the design based on these guidelines, it is essential to engage thoroughly with the distributor’s application engineer.

7. Many chip distributors impose strict time limits on providing quality layout recommendations. Often, the solutions they offer are tailored for “first-level customers” who utilize the device.

8. In the realm of signal integrity (SI) design, ensuring the signal integrity of new devices is particularly crucial. Following the distributor’s fundamental guidelines and considering the specific needs of each power and ground pin in the package will allow you to begin laying out and routing the OC48 card with the integrated DSP and microprocessor.

9. After finalizing the location and wiring of the high-frequency analog components, the remaining digital circuits can be positioned according to the grouping method illustrated in the block diagram.

10. It is vital to carefully design the following circuits: the placement of the PLL power filter circuit in the CPU, which is highly sensitive to analog signals; the voltage regulator for the local CPU core; and the reference voltage circuit for the “digital” microprocessor.

1. The electrical and manufacturing guidelines for digital wiring can be effectively implemented in the current design phase. The previously mentioned design considerations for signal integrity in high-speed digital buses and clock signals highlight specific wiring topology requirements for the processor bus, balanced T-lines, and timing delay matching of certain clock signal traces. Interestingly, some experts have proposed an updated recommendation: to add more termination resistors.

2. During the problem-solving process, it is natural to make adjustments at the layout stage. However, before initiating the PCB layout, a critical step is to verify the timing of the digital components in accordance with the layout plan. At this stage, a thorough DFM/DFT layout review of the board will help ensure that the design meets customer requirements.

3. Digital wiring for the OC48 card should begin with the SMD escape patterns for the power lines of digital devices and the digital section of the mixed-signal DSP. Use the shortest and widest printed traces permissible by the assembly process. For high-frequency devices, the printed power lines behave like small inductors, which can exacerbate power supply noise and lead to unwanted coupling between analog and digital circuits. The longer the power trace, the higher the inductance.

4. Employing digital bypass capacitors can optimize the layout and routing scheme. Essentially, fine-tune the placement of the bypass capacitors as necessary to facilitate installation and distribute them around both the digital section and the digital portion of the mixed-signal device. Utilize the same “shortest and widest trace” approach for routing the bypass capacitors.

5. When a power supply branch traverses a continuous plane (such as the 3.3V power plane on the OC48 interface card), the power supply pin and the bypass capacitor do not need to share the same outlet diagram, enabling the lowest possible inductance and ESR bypass. On mixed-signal PCBs like the OC48 interface card, pay special attention to the wiring of the power supply branch. It’s essential to place additional bypass capacitors in a matrix configuration throughout the card, even near passive components.

6. Once the power outlet diagram is finalized, you can proceed with automatic routing. The ATE test contacts on the OC48 card should be defined during the logic design phase. Ensure that ATE probes connect to 100% of the nodes. To facilitate ATE testing with the smallest probe size of 0.070 inches, the placement of breakout vias must be carefully reserved to prevent interruption of the power plane by via antipads.

7. If employing a split solution for power and ground planes, select a layer bias on the adjacent wiring layer parallel to the opening. Define restricted wiring areas on the adjacent layer based on the perimeter of the opening to prevent undesired wiring. If the traces must cross through the open area to another layer, ensure that the adjacent layer is a continuous ground plane. This approach will minimize the reflection path. While it’s beneficial for some digital signals to have bypass capacitors across the open power plane, bridging between digital and analog power planes is discouraged due to potential noise coupling through the bypass capacitors.

8. In mixed-signal PCB design, several cutting-edge automatic routing applications can effectively handle high-density multi-layer digital circuits. In the initial wiring phase, utilize 0.050-inch large via spacing at the SMD exit and consider the package type employed. In subsequent wiring stages, allow vias to be placed closer together to achieve the highest layout efficiency with the fewest vias. Given that the OC48 processor bus employs an enhanced star topology, it takes precedence during automatic routing.

If you have any PCB manufacturing needs, please do not hesitate to contact me.Contact me