Challenges and Innovations in PCB Board-Level Design

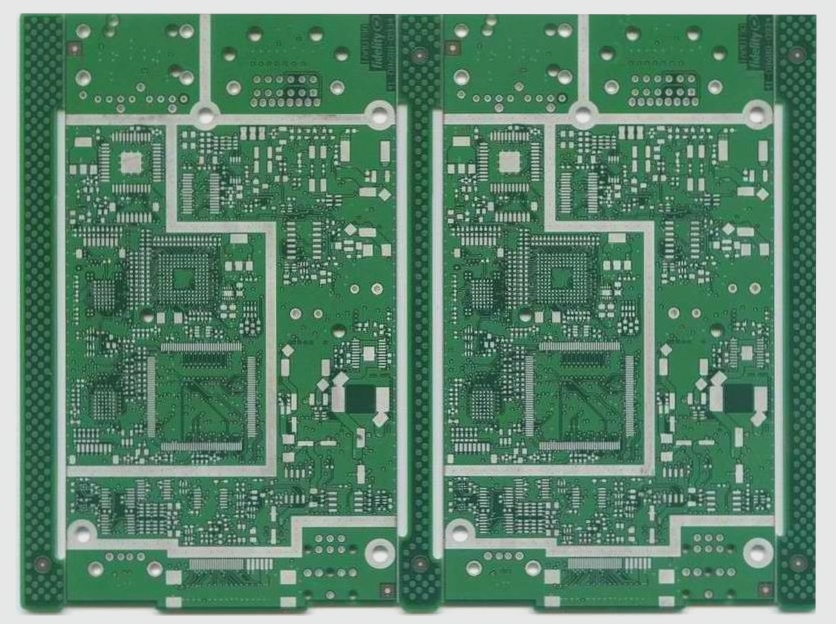

Today’s electronic PCB board designs are complex, integrating hardware and software to meet evolving technology demands. Engineers face challenges in dividing system functions efficiently, designing high-performance boards, and navigating the rapid pace of electronic advancements.

New Design Constraints

- Semiconductor processes reaching deep sub-micron levels

- Diverse chip packages with high-density and miniaturization

- Increased chip operating frequencies

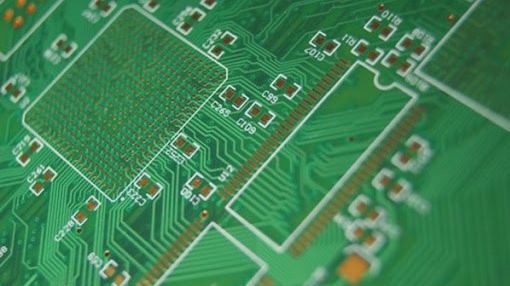

High-Speed Circuit Design

Designing high-speed digital circuits with fast clock frequencies and edges is crucial. Product miniaturization and high performance require navigating distribution effects from mixed-signal design techniques on the same board.

Addressing Design Challenges

To overcome challenges in high-speed circuit design, a real-time electrical rule-driven physical layout concept has been proposed. This approach integrates electrical requirements and physical implementations, offering a more efficient design process and improved quality control.

Mixed-Signal Design Solutions

As demands for miniaturization and high performance grow, mixed-signal design solutions combining digital-analog hybrid and radio frequency technologies have become essential. Collaboration among design teams and innovative design approaches help accelerate time-to-market for high-performance products.

Enhancing Design Efficiency

Utilizing powerful EDA tools, design teams can implement collaborative product development strategies, such as design reuse and parallel development. These approaches streamline the design cycle, enhance productivity, and meet market competition demands.

The Benefits of Derivative Technology in PCB Manufacturing

Derivative technology has revolutionized the way manufacturers develop PCB products, leading to improved efficiency and cost savings. By utilizing a single design process data, manufacturers can create products with varying functions and grades, ultimately enhancing PCB board quality.

One of the key advantages of derivative technology is its ability to enhance product flexibility and reliability. Manufacturers can now easily customize products to meet specific requirements, leading to a more diverse range of product offerings.

Furthermore, derivative technology optimizes the design process, resulting in faster production times and improved overall product quality. By streamlining the manufacturing process, manufacturers can reduce costs and deliver high-quality PCB products to the market.