Designing a Multilayer PCB for Electromagnetic Compatibility (EMC)

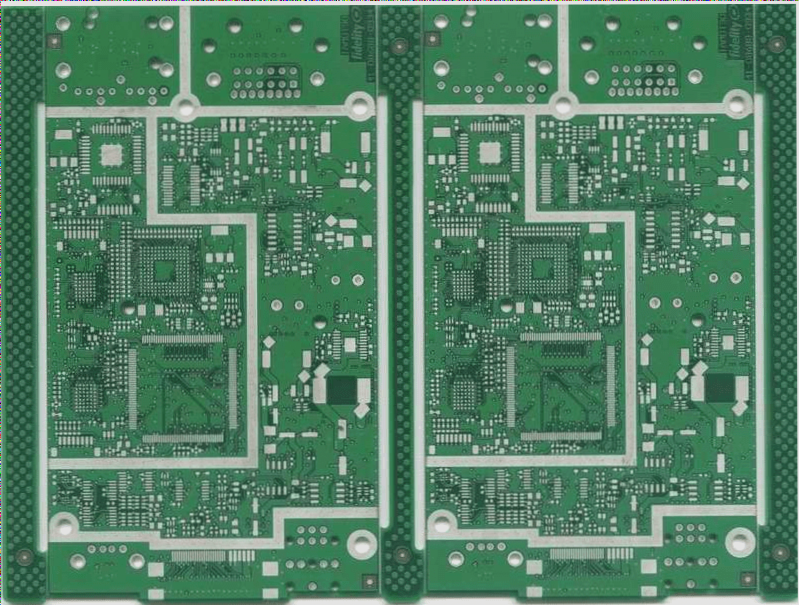

- Before creating a multilayer printed circuit board (PCB), it is crucial to define the electromagnetic compatibility (EMC) requirements. This includes factors like PCB size and design constraints.

- Choosing the right PCB structure, whether it’s a 4-layer, 6-layer, or higher-layer count PCB, depends on these requirements.

- Deciding on the placement of internal electrical layers and signal allocation across these layers defines the stack-up structure of the multilayer PCB.

- The stack-up configuration significantly impacts the PCB’s EMC performance by reducing electromagnetic interference (EMI).

Layer Selection and Stack-Up Structure

When designing a multilayer PCB, several factors come into play:

- More layers offer better routing options but also increase complexity.

- Symmetry in the laminate structure affects manufacturing costs and difficulty.

- Consider routing bottlenecks, wiring density, and special signal requirements.

- Placement of signal layers, power/ground layers, and high-speed signal layers is crucial.

- Multiple grounded internal layers can reduce ground impedance and interference.

- Ensure symmetry in the layer structure for balance and performance.

Common Stack-Up Structures

For a 4-layer PCB, common stack-up configurations include:

- Signal_1 (Top), GND, POWER, Signal_2 (Bottom).

- Signal_1 (Top), POWER, GND, Signal_2 (Bottom).

- POWER (Top), Signal_1, GND, Signal_2 (Bottom).

Choosing Between PCB Stack-Up Options: A Comprehensive Guide

When it comes to designing a PCB, selecting the right stack-up option is crucial for optimal performance. Let’s delve into the differences between options 1 and 2 to help you make an informed decision.

Option 1: 4-Layer Board Structure

- Preferred choice for most designs where components are placed on the top layer.

- Bottom layer usually has fewer signal traces, allowing for effective coupling with the power layer.

Option 2: Alternate Choice for Specific Designs

- Suitable when components are placed on both the top and bottom layers.

- May be more appropriate if the dielectric thickness between power and ground layers is large.

Exploring 6-Layer Board Examples

Let’s examine different stack-up structures for a 6-layer board to understand how they impact performance:

Scheme 1

- Offers 4 signal layers and 2 internal power/ground layers.

- Drawbacks include spaced-apart power and ground layers, leading to poor coupling.

Scheme 2

- Provides better coupling between power and ground layers compared to Scheme 1.

- Signal isolation issues persist due to adjacent signal layers.

Scheme 3

- Improves upon previous schemes by reducing signal layers and adding an internal power/ground layer.

- Ensures tight coupling between power and ground layers, enhancing signal isolation and reducing crosstalk.

While no single stack-up structure fits all design requirements, prioritizing principles like tight coupling between power and ground layers and positioning high-speed signal layers appropriately is crucial for optimal performance. If you’re in need of PCB manufacturing services, feel free to contact me.