1. EMI Generation and Suppression Principles

2. EMI in printed circuit board (PCB) design is caused by sources of electromagnetic interference that transfer energy to sensitive systems through coupling paths. It manifests in three basic forms: conduction through wires or common grounds, radiation through space, or coupling through near-fields. The harm of EMI is evident in signal transmission quality reduction, interference, or potential circuit and equipment damage, preventing compliance with electromagnetic compatibility standards. To mitigate EMI, the design of digital circuits should adhere to the following principles:

1.1 Decompose EMC/EMI technical specifications into individual board circuits for hierarchical control.

1.2 Address EMI from its three elements—interference sources, energy coupling paths, and sensitive systems—to ensure a flat frequency response and stable circuit operation.

1.3 Initiate EMC/EMI design considerations from the equipment’s front-end design phase to minimize overall design costs.

2. EMI control technology of digital circuit PCB board

When addressing various forms of EMI, it is crucial to analyze specific issues. In digital circuit PCB board design, EMI control can be effectively implemented from several perspectives.

2.1 Device Selection

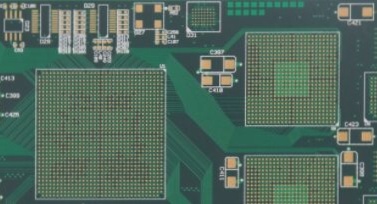

In EMI design, the speed of the selected devices should be prioritized. Substituting a device with a rise time of 5ns for one with a 2.5ns rise time can increase EMI approximately fourfold. The radiated intensity of EMI relates to the square of the frequency, determined by the signal rise time (Tr) rather than the signal frequency itself: fknee = 0.35/Tr. Within the 30MHz to several GHz frequency range, wavelengths are short, causing even brief circuit board wiring to act as transmitting antennas. High EMI levels can disrupt circuit functionality. Therefore, while ensuring circuit performance requirements, opt for slower chips where possible, accompanied by suitable driving/receiving circuits. Additionally, consider the impact of device packaging on signal due to parasitic inductance and capacitance of lead pins; SMD devices generally exhibit lower parasitics than through-hole devices, with BGA packages typically having fewer parasitics than QFP packages.

2.2 Connector Selection and Signal Terminal Definition

Connectors are pivotal for high-speed signal transmission but also represent a vulnerable point for EMI. When designing connector terminals, include more ground pins to minimize signal-to-ground distances, reduce the effective signal loop area generating connector radiation, and provide a low-impedance return path. Where necessary, isolate critical signals using ground pins.

2.3 Laminate Design

If economically feasible, increase the number of ground layers and position signal layers adjacent to ground plane layers to lessen EMI radiation. For high-speed PCBs, closely coupled power and ground planes decrease power supply impedance, thereby reducing EMI.

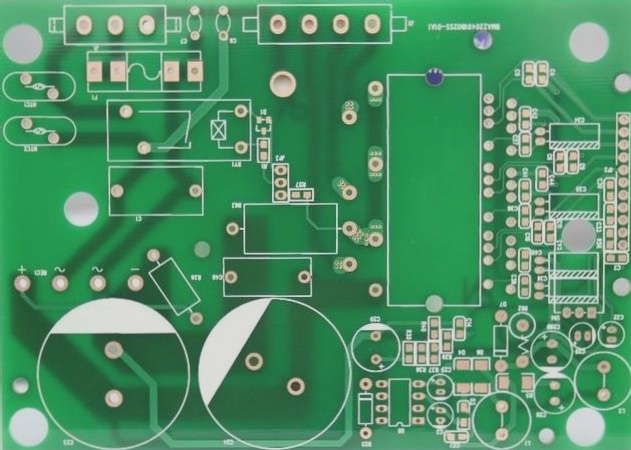

2.4 Layout

Adopting a rational layout aligned with signal current flow minimizes signal interference. Key layout principles encompass: (1) Separating analog and digital circuits to prevent digital signal interference with analog signals; (2) Isolating clock lines—significant sources of interference—away from sensitive circuits and keeping clock lines short; (3) Avoiding central placement of high-current, high-power-consuming circuits on the board, while considering heat dissipation and radiation effects; (4) Preferably placing connectors on one board side, away from high-frequency circuits; (5) Positioning input/output circuits near corresponding connectors and decoupling capacitors near respective power supply pins; (6) Carefully planning power partitioning feasibility and placing multi-power devices at power splitting area boundaries to effectively mitigate plane splitting’s impact on EMI; (7) Maintaining continuity in reflow plane paths without division.

2.5 Wiring

Effective wiring practices include: (1) Impedance control to manage transmission line characteristics of high-speed signal lines, preventing signal reflection, overshoot, ringing, and reducing EMI radiation; (2) Segmenting signals based on EMI radiation intensity and sensitivity, separating interference sources from sensitive systems to minimize coupling; (3) Stringently regulating trace length, via count, cross-partitions, terminations, wiring layers, and return paths of clock signals, particularly high-speed ones; (4) Focusing on signal loops—controlling signal flow paths to minimize loop area, directing low-frequency currents through resistive paths and high-frequency currents through inductive paths for differential mode radiation reduction; (5) Ensuring optimal coupling of high-speed differential signal traces, meeting requirements for striplines, microstrip lines, and their reference planes; (6) Short and wide decoupling capacitor leads, keeping all signal traces away from board edges, and selecting suitable network topologies for multi-point connections to curb signal reflections and EMI emissions.

2.6 Power Plane Split Processing

Efficient power plane management involves: (1) Segmenting the power supply layer into distinct sub-supply areas within the main power plane, ensuring each area maintains continuity and sufficient copper foil width, with the dividing line typically 20-50 mil wide to reduce radiation gaps; (2) Carefully managing ground plane layer segmentation to retain integrity; if division is unavoidable, distinguishing digital, analog, and noise grounds, connecting them externally through a common ground point at the outlet to lessen power supply fringe radiation; implementing the 20H design principle to reduce fringe field radiation intensity by enlarging ground plane size 20 times the power plane size.

3. Other EMI Control Methods

3.1 Power System Design

Designing a low-impedance power system ensures power distribution system impedance in frequencies below fknee remains lower than target impedance. Employing filters controls conducted interference, while proper power supply decoupling with capacitors aids reliable chip operation, reducing high-frequency noise in the power supply and EMI.

3.2 Grounding

Effective grounding is pivotal for overall board EMI reduction: (1) Utilize single-point, multi-point, or hybrid grounding methods; (2) Segment digital, analog, and noise grounds, establishing suitable common ground points; (3) In double-sided designs lacking a dedicated ground layer, thoughtfully design the ground grid, ensuring adequate widths for ground, power, and signal traces, considering large-area paving methods while ensuring contiguous large-area ground on the same layer; (4) For multi-layer boards, ensure a ground plane layer exists to minimize common ground impedance.

3.3 Series Damping Resistor

Series-inserting small-value resistors (typically 22-33Ω) at key signal outputs, if timing permits, mitigates interference by slowing rise/fall times, smoothing overshoot/undershoot signals, reducing high-frequency harmonic amplitudes, and effectively suppressing EMI.

3.4 Shielding

Apply EMI shielding materials or meshes for critical devices or signal lines; shield key signals using strip lines or isolated ground wires on both sides.

3.5 Spread Spectrum

Implement spread spectrum modulation to expand signal energy across a wider frequency range, effectively reducing emissions by 7 to 20 dB without significantly increasing clock signal jitter.

3.6 EMI Analysis and Testing

Conduct simulation analysis post-PCB wiring completion using EMI simulation software to evaluate EMC/EMI compliance with relevant standards; perform scanning tests with electromagnetic radiation scanners post-assembly.

4. Summary

As new high-speed chips continue to evolve, carrying increasingly higher signal frequencies, PCB design faces growing EMI challenges. Successful EMC/EMI design necessitates ongoing exploration and innovation.

2. EMI in printed circuit board (PCB) design is caused by sources of electromagnetic interference that transfer energy to sensitive systems through coupling paths. It manifests in three basic forms: conduction through wires or common grounds, radiation through space, or coupling through near-fields. The harm of EMI is evident in signal transmission quality reduction, interference, or potential circuit and equipment damage, preventing compliance with electromagnetic compatibility standards. To mitigate EMI, the design of digital circuits should adhere to the following principles:

1.1 Decompose EMC/EMI technical specifications into individual board circuits for hierarchical control.

1.2 Address EMI from its three elements—interference sources, energy coupling paths, and sensitive systems—to ensure a flat frequency response and stable circuit operation.

1.3 Initiate EMC/EMI design considerations from the equipment’s front-end design phase to minimize overall design costs.

2. EMI control technology of digital circuit PCB board

When addressing various forms of EMI, it is crucial to analyze specific issues. In digital circuit PCB board design, EMI control can be effectively implemented from several perspectives.

2.1 Device Selection

In EMI design, the speed of the selected devices should be prioritized. Substituting a device with a rise time of 5ns for one with a 2.5ns rise time can increase EMI approximately fourfold. The radiated intensity of EMI relates to the square of the frequency, determined by the signal rise time (Tr) rather than the signal frequency itself: fknee = 0.35/Tr. Within the 30MHz to several GHz frequency range, wavelengths are short, causing even brief circuit board wiring to act as transmitting antennas. High EMI levels can disrupt circuit functionality. Therefore, while ensuring circuit performance requirements, opt for slower chips where possible, accompanied by suitable driving/receiving circuits. Additionally, consider the impact of device packaging on signal due to parasitic inductance and capacitance of lead pins; SMD devices generally exhibit lower parasitics than through-hole devices, with BGA packages typically having fewer parasitics than QFP packages.

2.2 Connector Selection and Signal Terminal Definition

Connectors are pivotal for high-speed signal transmission but also represent a vulnerable point for EMI. When designing connector terminals, include more ground pins to minimize signal-to-ground distances, reduce the effective signal loop area generating connector radiation, and provide a low-impedance return path. Where necessary, isolate critical signals using ground pins.

2.3 Laminate Design

If economically feasible, increase the number of ground layers and position signal layers adjacent to ground plane layers to lessen EMI radiation. For high-speed PCBs, closely coupled power and ground planes decrease power supply impedance, thereby reducing EMI.

2.4 Layout

Adopting a rational layout aligned with signal current flow minimizes signal interference. Key layout principles encompass: (1) Separating analog and digital circuits to prevent digital signal interference with analog signals; (2) Isolating clock lines—significant sources of interference—away from sensitive circuits and keeping clock lines short; (3) Avoiding central placement of high-current, high-power-consuming circuits on the board, while considering heat dissipation and radiation effects; (4) Preferably placing connectors on one board side, away from high-frequency circuits; (5) Positioning input/output circuits near corresponding connectors and decoupling capacitors near respective power supply pins; (6) Carefully planning power partitioning feasibility and placing multi-power devices at power splitting area boundaries to effectively mitigate plane splitting’s impact on EMI; (7) Maintaining continuity in reflow plane paths without division.

2.5 Wiring

Effective wiring practices include: (1) Impedance control to manage transmission line characteristics of high-speed signal lines, preventing signal reflection, overshoot, ringing, and reducing EMI radiation; (2) Segmenting signals based on EMI radiation intensity and sensitivity, separating interference sources from sensitive systems to minimize coupling; (3) Stringently regulating trace length, via count, cross-partitions, terminations, wiring layers, and return paths of clock signals, particularly high-speed ones; (4) Focusing on signal loops—controlling signal flow paths to minimize loop area, directing low-frequency currents through resistive paths and high-frequency currents through inductive paths for differential mode radiation reduction; (5) Ensuring optimal coupling of high-speed differential signal traces, meeting requirements for striplines, microstrip lines, and their reference planes; (6) Short and wide decoupling capacitor leads, keeping all signal traces away from board edges, and selecting suitable network topologies for multi-point connections to curb signal reflections and EMI emissions.

2.6 Power Plane Split Processing

Efficient power plane management involves: (1) Segmenting the power supply layer into distinct sub-supply areas within the main power plane, ensuring each area maintains continuity and sufficient copper foil width, with the dividing line typically 20-50 mil wide to reduce radiation gaps; (2) Carefully managing ground plane layer segmentation to retain integrity; if division is unavoidable, distinguishing digital, analog, and noise grounds, connecting them externally through a common ground point at the outlet to lessen power supply fringe radiation; implementing the 20H design principle to reduce fringe field radiation intensity by enlarging ground plane size 20 times the power plane size.

3. Other EMI Control Methods

3.1 Power System Design

Designing a low-impedance power system ensures power distribution system impedance in frequencies below fknee remains lower than target impedance. Employing filters controls conducted interference, while proper power supply decoupling with capacitors aids reliable chip operation, reducing high-frequency noise in the power supply and EMI.

3.2 Grounding

Effective grounding is pivotal for overall board EMI reduction: (1) Utilize single-point, multi-point, or hybrid grounding methods; (2) Segment digital, analog, and noise grounds, establishing suitable common ground points; (3) In double-sided designs lacking a dedicated ground layer, thoughtfully design the ground grid, ensuring adequate widths for ground, power, and signal traces, considering large-area paving methods while ensuring contiguous large-area ground on the same layer; (4) For multi-layer boards, ensure a ground plane layer exists to minimize common ground impedance.

3.3 Series Damping Resistor

Series-inserting small-value resistors (typically 22-33Ω) at key signal outputs, if timing permits, mitigates interference by slowing rise/fall times, smoothing overshoot/undershoot signals, reducing high-frequency harmonic amplitudes, and effectively suppressing EMI.

3.4 Shielding

Apply EMI shielding materials or meshes for critical devices or signal lines; shield key signals using strip lines or isolated ground wires on both sides.

3.5 Spread Spectrum

Implement spread spectrum modulation to expand signal energy across a wider frequency range, effectively reducing emissions by 7 to 20 dB without significantly increasing clock signal jitter.

3.6 EMI Analysis and Testing

Conduct simulation analysis post-PCB wiring completion using EMI simulation software to evaluate EMC/EMI compliance with relevant standards; perform scanning tests with electromagnetic radiation scanners post-assembly.

4. Summary

As new high-speed chips continue to evolve, carrying increasingly higher signal frequencies, PCB design faces growing EMI challenges. Successful EMC/EMI design necessitates ongoing exploration and innovation.