Importance of Power Integrity in High-Speed PCB Design

In PCB design, signal quality is a top priority, but focusing solely on signal lines while neglecting power and ground can lead to issues, especially in high-speed designs. In China, where high-speed designs are prevalent, the impact of power integrity on signal quality cannot be ignored.

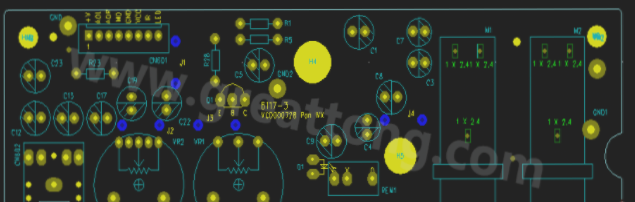

Decoupling Capacitor Optimization

Adding decoupling capacitors between the power supply and ground is common practice to reduce system noise. However, determining the number of capacitors, their capacitance values, and placement is crucial for managing system impedance effectively. In high-speed designs, considering the parasitic parameters of capacitors is essential to ensure optimal performance.

Ground Bounce Challenges

Ground bounce, caused by rapid data exchange in high-speed devices, can lead to power instability issues. Minimizing inductance in power and ground distribution is key to mitigating ground bounce. As devices evolve, reducing inductance through array configurations and shorter wiring becomes increasingly important.

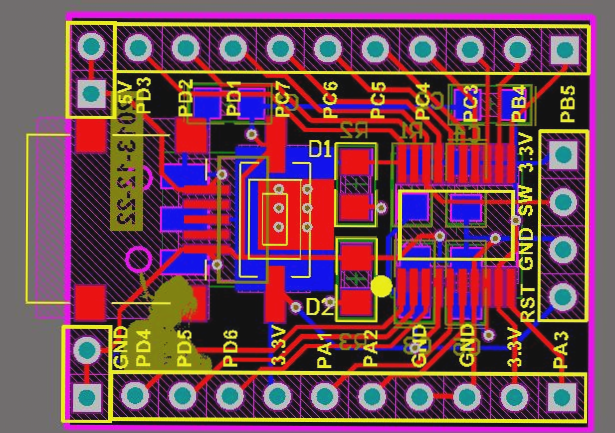

Optimizing Power Distribution

Controlling impedance in the power supply system is vital for ensuring power integrity in PCB layouts. Lower impedance results in reduced noise and voltage loss, enhancing overall performance. Establishing target impedance levels and adjusting circuit factors accordingly can help achieve optimal power distribution.