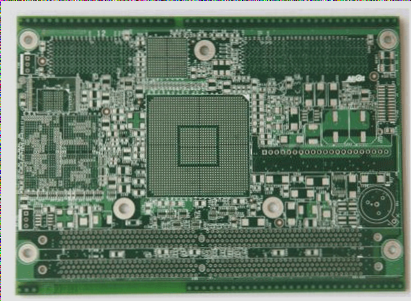

1. For the placement and installation of capacitors in PCB design, the primary consideration is the installation distance. The capacitor with the lowest capacitance exhibits the highest resonant frequency and the smallest decoupling radius, necessitating its placement closest to the chip. Capacitors with larger capacitance can be positioned further away, while those with the largest capacitance are generally found on the outermost layer. Nevertheless, all capacitors intended for decoupling the chip should be placed as near to the chip as possible.

2. Another important aspect to consider is that capacitors should be evenly distributed around the chip, and this applies to each capacitance level. Typically, the arrangement of the power and ground pins is factored into the chip design, resulting in an even distribution around all four sides of the chip. Consequently, voltage disturbances can occur around the entire chip, necessitating that decoupling is uniformly applied across the chip area. For example, if 680pF capacitors are situated at the upper part of the chip, the decoupling radius issue could hinder effective decoupling of voltage disturbances at the lower part.

3. Capacitor installation involves pulling out a short lead from the pad, which is then connected to the power plane via a via hole. The same procedure applies to the ground terminal. The current loop through the capacitor follows this path: power plane -> via -> lead-out line -> pad -> capacitor -> pad -> lead-out line -> via -> ground plane. Figure 2 visually illustrates this current reflux path.

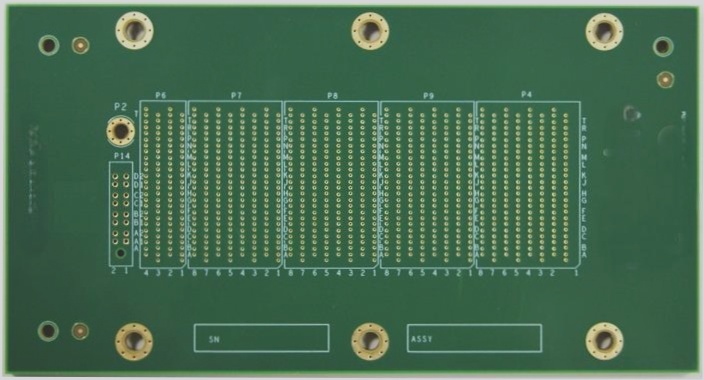

1. The first method involves extending a long lead wire from the pad to the via hole, which introduces significant parasitic inductance. This approach should be avoided as it represents the least favorable installation method.

2. The second method entails drilling holes at both ends of the pad adjacent to it. This configuration has a considerably smaller loop area than the first method, resulting in lower parasitic inductance, which is acceptable.

3. The third approach involves drilling holes on the side of the pad, further minimizing the loop area and reducing parasitic inductance even more than the second method, making it a superior choice.

4. The fourth method features holes on both sides of the pad. Compared to the third method, this configuration connects each end of the capacitor in parallel to the power and ground planes through vias, resulting in lower parasitic inductance. If space allows, this method is recommended.

5. The final method consists of directly drilling holes on the pads, which yields the lowest parasitic inductance; however, this may present challenges during soldering. Whether to use this method depends on the processing capabilities and techniques available.

6. The third and fourth methods are preferred.

7. It’s important to emphasize: to save space, some PCB design engineers may allow multiple capacitors to share common vias. This practice should be strictly avoided. Instead, it’s advisable to explore optimizing the capacitor layout and reducing the overall number of capacitors.

8. Since wider PCB traces result in lower inductance, the lead-out trace from the pad to the via should be as wide as possible. If feasible, it should match the width of the pad. For example, even with a capacitor in a 0402 package, a 20 mil-wide lead wire can be utilized. The arrangement of lead wires and vias is illustrated in Figure 4, so pay attention to the various dimensions shown.