1. Nowadays, CMOS technology enables FPGA devices to incorporate multiple I/O interfaces.

2. Simultaneously, low power consumption has emerged as a mainstream concept for high-speed I/O interfaces in recent years.

3. The most effective strategy for reducing power consumption is to lower the operating voltage; however, this reduction leads to a diminished noise margin for the I/O interface.

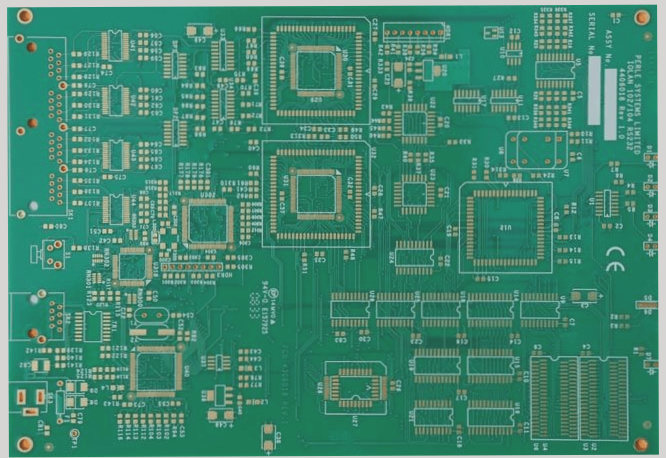

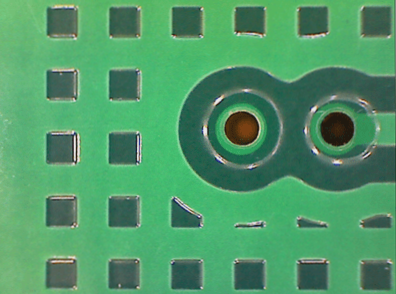

4. Therefore, it is essential for FPGA users to quantify the system-level synchronous switching noise (SSN) present in the chip, package, and PCB environment.

5. This article systematically introduces SSN, with a focus on the SSN generated by FPGA output buffering.

6. This type of noise is commonly referred to as Synchronous Switching Output Noise (SSO), which differs from the SSN produced by input buffering.

7. We will explore the causes of system-level SSO and propose a layered modeling approach to address it.

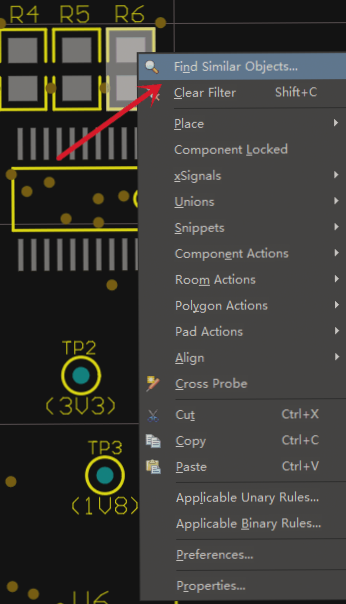

8. Additionally, the article explains how to connect the SSO model with frequency domain and time domain measurements, providing several PCB design strategies to mitigate SSO.

—

Let me know if you need any further adjustments!