What a wonderful thing it would be if high-speed PCB board design could be as simple as connecting schematic nodes, and as beautiful as it looks on a computer monitor. However, unless designers are new to PCB design, or are extremely lucky, the actual PCB design is usually not as easy as the circuit design they are engaged in. PCB board designers face many new challenges until the design can finally work and someone can affirm its performance. This is exactly the current state of high-speed PCB board design – design rules and design guidelines are constantly evolving, and if you’re lucky, they lead to a successful solution. The vast majority of PCB boards are schematic designers who are proficient in the working principle and interaction of PCB components and the various data transmission standards that constitute the input and output of the circuit board. The result of collaboration between layout designers on what happens when the wires are converted to printed circuit copper wires. Often, the schematic designer is responsible for the success or failure of the final board. However, the more a schematic designer knows about layout techniques, the more opportunity there is to avoid major problems. If the design includes a high density of FPGAs, there are likely to be many challenges ahead of a well-designed schematic. Including hundreds of input and output ports, operating frequencies in excess of 500MHz (possibly higher in some designs), solder ball spacing as small as half a millimeter, etc. mutual influence.

Concurrent switching noise

The challenge is likely to be what is known as concurrent switching noise (SSN) or concurrent switching output (SSO). The high volume of high-frequency data streams will create issues such as ringing and crosstalk on the data lines, as well as ground bounce and power supply noise on the power and ground planes that affect overall board performance. To address ringing and crosstalk on high-speed data lines, switching to differential signaling is a good step. Since one wire on the differential pair is the sink and the other is the source, the inductive effects are essentially eliminated. When transferring data using differential pairs, it helps to reduce the “bounce” noise from induced currents in the return path because the current is kept local. For radio frequencies up to hundreds of MHz or even several GHz, signal theory suggests that signal power can be delivered when impedances are matched. When the transmission line is not well matched, there will be reflections, only a part of the signal will be transmitted from the sender to the receiver, while other parts will bounce back and forth between the sender and receiver. How well a differential signal is implemented on a PCB will play a big role in impedance matching (among other things).

Differential trace design

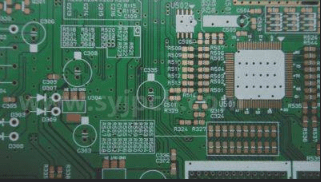

The differential trace design is based on the principle of an impedance-controlled PCB board. Its model is somewhat like a coaxial cable. On a controlled impedance PCB, the metal plane layer acts as a shield, the insulator is an FR4 laminate, and the conductors are the signal trace pairs (see Figure 1). The average dielectric constant of FR4 is between 4.2 and 4.5. Unaware of manufacturing errors may lead to over-etching of copper lines, eventually resulting in impedance errors. The method of calculating PCB trace impedance is to use a field analysis program (usually two-dimensional, sometimes three-dimensional), which requires the use of finite elements to directly solve Maxwell’s equations for the entire PCB batch. The software can analyze EMI effects based on trace spacing, trace width, trace thickness, and insulation height. The 100Ω characteristic impedance has become the industry standard value for differential connection cables. A 100Ω differential line can be made with two 50Ω single-ended lines of equal length. Since the two traces are close to each other, field coupling between the traces will reduce the differential mode impedance of the traces. To maintain the 100Ω impedance, the width of the trace has to be reduced a bit. As a result, the common-mode impedance of each wire in a 100Ω differential pair will be slightly higher than 50Ω. The size of the trace and the material used theoretically determine the impedance, but vias, connectors, and even device pads will introduce impedance discontinuities in the signal path. It’s usually not possible without these things. Sometimes, for a more reasonable layout and wiring, it is necessary to increase the number of layers on the PCB or to add functions such as buried vias. Buried vias only connect some layers of the PCB board, but while solving the problem of transmission lines, it also increases the cost of making the board. But sometimes there is no choice at all. As signal speeds get faster and space gets smaller, additional demands like buried vias start to increase, and these should be a cost factor for PCB board solutions. In stripline routing, the signals are sandwiched by FR-4 material. In the microstrip line, a conductor is exposed to the air. Because of the dielectric constant of air (Er= 1), the top layer is suitable for routing some critical signals, such as clock signals or high-frequency SERial-DESerial (SERDES) signals. Microstrip routing should be coupled to an underlying ground plane that reduces electromagnetic interference (EMI) by absorbing some of the electromagnetic field lines. In a stripline, all electromagnetic field lines are coupled to the reference plane above and below, which greatly reduces EMI. If possible, you should try not to use broadside coupled stripline designs. This structure is susceptible to differential noise coupled in the reference plane. In addition, balanced manufacturing of the PCB board is required, which is difficult to control. In general, it is relatively easy to control the spacing between lines on the same layer.

Decoupling and Bypass Capacitors

Another important aspect of determining whether the actual performance of the PCB board is as expected needs to be controlled by adding decoupling and bypass capacitors. Adding decoupling capacitors helps reduce the inductance between the power and ground planes of the PCB and helps control the impedance of signals and ICs throughout the PCB. Bypass capacitors help provide a clean power supply to the FPGA (provides a charge bank). The traditional rule is that decoupling capacitors should be placed wherever PCB board routing is convenient, and the number of FPGA power pins determines the number of decoupling capacitors. However, the ultra-high switching speed of FPGAs completely breaks this stereotype. In a typical FPGA board design, a capacitor close to the power supply provides frequency compensation for current changes in the load. To provide low-frequency filtering and prevent supply voltage droop, use large decoupling capacitors. The voltage drop is due to a lag in the response of the regulator when the designed circuit starts up. Such large capacitors are usually electrolytic capacitors with better low-frequency responses, and their frequency response ranges from DC to several hundred kHz. Every FPGA output change requires charging and discharging the signal lines, which requires energy. The function of the bypass capacitor is to provide local energy storage over a wide frequency range. In addition, small capacitors with small series inductance are required to provide high-speed current for high-frequency transients. The slow-responding large capacitor continues to supply current after the high-frequency capacitor energy is consumed. A large amount of current transients on the power bus increases the complexity of the FPGA design. Such current transients are usually associated with SSO/SSN. Inserting capacitors with very low inductance will provide localized high-frequency energy that can be used to cancel switching current noise on the power bus. This decoupling capacitor, which prevents high-frequency currents from entering the device power supply, must be very close to the FPGA (less than 1cm). Sometimes many small capacitors are connected together in parallel to act as local energy storage for the device and to respond quickly to changing current demands. In general, the traces for decoupling capacitors should be short, including vertical distances in vias. Adding even a small amount will increase the inductance of the wire, reducing the effect of decoupling.

other technologies

As signal speeds have increased, it has become increasingly difficult to easily transfer data across circuit boards. Several other techniques can be used to further improve the performance of the PCB board. The first and obvious method is a simple device layout. It’s common sense to design short and direct paths for critical connections, but don’t underestimate this. Why go to the trouble of adjusting the signals on the board when simple strategies can do the trick? An almost equally brief approach is to consider the width of the signal lines. When the data rate is as high as 622MHz and even higher, the skin effect of signaling becomes more and more prominent. When the distance is long, very thin traces (such as 4 or 5 mils) on the PCB will form a large attenuation of the signal, just like a low-pass filter with no attenuation designed, its attenuation increases with frequency. The longer the backplane, the higher the frequency, and the wider the signal line should be. For backplane traces longer than 20 inches, the trace width should be 10 or 12 mils. Usually, the critical signal on the board is the clock signal. When clock lines are too long or poorly designed, they can amplify jitter and skew downstream, especially as speed increases. Multiple layers to transmit the clock should be avoided, and there should be no vias on the clock lines, as vias will increase impedance variations and reflections. If an inner layer must be used to route the clock, then the upper and lower layers should use ground planes to reduce latency. When designing with an FPGA PLL, noise on the power planes can increase PLL jitter. If this is critical, a “power island” can be created for the PLL, which can be used to isolate the PLL analog and digital power supplies using thicker etchings in the metal planes.

For signals with rates above 2Gbps, a more expensive solution must be considered. At such high frequencies, the thickness of the backplane and via design can have a significant impact on signal integrity. Works well when the thickness of the backing plate does not exceed 0.200 inches. When high-speed signals are used on the PCB, the number of layers should be as few as possible to limit the number of vias. In thick boards, the vias connecting the signal layers are longer and will form transmission line branches on the signal path. Using buried vias can solve this problem, but the manufacturing cost is high. Another option is to use a low-loss dielectric material such as Rogers 4350, GETEK, or ARLON. These materials can be nearly double the cost of FR4 materials, but sometimes this is the choice. There are other design techniques for FPGAs that provide some choice of I/O locations. In critical high-speed SERDES designs, SERDES I/Os can be isolated by reserving (but not using) adjacent I/O pins. For example, a 3×3 or 5×5 BGA ball area can be reserved relative to SERDES Rx and Tx, VCCRX# and VCCTX#, and ball position. Or if possible, keep the entire I/O group close to the SERDES. If there are no I/O constraints in the design, these techniques can bring benefits without adding cost. Also one of the ways is to refer to the reference board provided by the FPGA manufacturer. Most manufacturers provide source layout information for reference boards, although special requests may be required due to proprietary information issues. These boards often contain standard high-speed I/O interfaces that FPGA manufacturers need to characterize their devices. Keep in mind, however, that these boards are often designed for multiple purposes and may not necessarily match a specific design need. Nonetheless, they can be used as a starting point for creating solutions.

Summary of this article

Of course, this article only touches on some basic concepts. Any of the topics covered here could be discussed in an entire book. The key is to figure out what the goal is before investing a lot of time and effort into PCB layout design. Once the layout is complete, a redesign can cost a lot of time and money, even with a slight adjustment to the width of the traces. You cannot rely on PCB board layout engineers to make designs that meet actual needs. The schematic designer is always there to provide guidance, make smart choices, and take responsibility for the success of the solution.

Concurrent switching noise

The challenge is likely to be what is known as concurrent switching noise (SSN) or concurrent switching output (SSO). The high volume of high-frequency data streams will create issues such as ringing and crosstalk on the data lines, as well as ground bounce and power supply noise on the power and ground planes that affect overall board performance. To address ringing and crosstalk on high-speed data lines, switching to differential signaling is a good step. Since one wire on the differential pair is the sink and the other is the source, the inductive effects are essentially eliminated. When transferring data using differential pairs, it helps to reduce the “bounce” noise from induced currents in the return path because the current is kept local. For radio frequencies up to hundreds of MHz or even several GHz, signal theory suggests that signal power can be delivered when impedances are matched. When the transmission line is not well matched, there will be reflections, only a part of the signal will be transmitted from the sender to the receiver, while other parts will bounce back and forth between the sender and receiver. How well a differential signal is implemented on a PCB will play a big role in impedance matching (among other things).

Differential trace design

The differential trace design is based on the principle of an impedance-controlled PCB board. Its model is somewhat like a coaxial cable. On a controlled impedance PCB, the metal plane layer acts as a shield, the insulator is an FR4 laminate, and the conductors are the signal trace pairs (see Figure 1). The average dielectric constant of FR4 is between 4.2 and 4.5. Unaware of manufacturing errors may lead to over-etching of copper lines, eventually resulting in impedance errors. The method of calculating PCB trace impedance is to use a field analysis program (usually two-dimensional, sometimes three-dimensional), which requires the use of finite elements to directly solve Maxwell’s equations for the entire PCB batch. The software can analyze EMI effects based on trace spacing, trace width, trace thickness, and insulation height. The 100Ω characteristic impedance has become the industry standard value for differential connection cables. A 100Ω differential line can be made with two 50Ω single-ended lines of equal length. Since the two traces are close to each other, field coupling between the traces will reduce the differential mode impedance of the traces. To maintain the 100Ω impedance, the width of the trace has to be reduced a bit. As a result, the common-mode impedance of each wire in a 100Ω differential pair will be slightly higher than 50Ω. The size of the trace and the material used theoretically determine the impedance, but vias, connectors, and even device pads will introduce impedance discontinuities in the signal path. It’s usually not possible without these things. Sometimes, for a more reasonable layout and wiring, it is necessary to increase the number of layers on the PCB or to add functions such as buried vias. Buried vias only connect some layers of the PCB board, but while solving the problem of transmission lines, it also increases the cost of making the board. But sometimes there is no choice at all. As signal speeds get faster and space gets smaller, additional demands like buried vias start to increase, and these should be a cost factor for PCB board solutions. In stripline routing, the signals are sandwiched by FR-4 material. In the microstrip line, a conductor is exposed to the air. Because of the dielectric constant of air (Er= 1), the top layer is suitable for routing some critical signals, such as clock signals or high-frequency SERial-DESerial (SERDES) signals. Microstrip routing should be coupled to an underlying ground plane that reduces electromagnetic interference (EMI) by absorbing some of the electromagnetic field lines. In a stripline, all electromagnetic field lines are coupled to the reference plane above and below, which greatly reduces EMI. If possible, you should try not to use broadside coupled stripline designs. This structure is susceptible to differential noise coupled in the reference plane. In addition, balanced manufacturing of the PCB board is required, which is difficult to control. In general, it is relatively easy to control the spacing between lines on the same layer.

Decoupling and Bypass Capacitors

Another important aspect of determining whether the actual performance of the PCB board is as expected needs to be controlled by adding decoupling and bypass capacitors. Adding decoupling capacitors helps reduce the inductance between the power and ground planes of the PCB and helps control the impedance of signals and ICs throughout the PCB. Bypass capacitors help provide a clean power supply to the FPGA (provides a charge bank). The traditional rule is that decoupling capacitors should be placed wherever PCB board routing is convenient, and the number of FPGA power pins determines the number of decoupling capacitors. However, the ultra-high switching speed of FPGAs completely breaks this stereotype. In a typical FPGA board design, a capacitor close to the power supply provides frequency compensation for current changes in the load. To provide low-frequency filtering and prevent supply voltage droop, use large decoupling capacitors. The voltage drop is due to a lag in the response of the regulator when the designed circuit starts up. Such large capacitors are usually electrolytic capacitors with better low-frequency responses, and their frequency response ranges from DC to several hundred kHz. Every FPGA output change requires charging and discharging the signal lines, which requires energy. The function of the bypass capacitor is to provide local energy storage over a wide frequency range. In addition, small capacitors with small series inductance are required to provide high-speed current for high-frequency transients. The slow-responding large capacitor continues to supply current after the high-frequency capacitor energy is consumed. A large amount of current transients on the power bus increases the complexity of the FPGA design. Such current transients are usually associated with SSO/SSN. Inserting capacitors with very low inductance will provide localized high-frequency energy that can be used to cancel switching current noise on the power bus. This decoupling capacitor, which prevents high-frequency currents from entering the device power supply, must be very close to the FPGA (less than 1cm). Sometimes many small capacitors are connected together in parallel to act as local energy storage for the device and to respond quickly to changing current demands. In general, the traces for decoupling capacitors should be short, including vertical distances in vias. Adding even a small amount will increase the inductance of the wire, reducing the effect of decoupling.

other technologies

As signal speeds have increased, it has become increasingly difficult to easily transfer data across circuit boards. Several other techniques can be used to further improve the performance of the PCB board. The first and obvious method is a simple device layout. It’s common sense to design short and direct paths for critical connections, but don’t underestimate this. Why go to the trouble of adjusting the signals on the board when simple strategies can do the trick? An almost equally brief approach is to consider the width of the signal lines. When the data rate is as high as 622MHz and even higher, the skin effect of signaling becomes more and more prominent. When the distance is long, very thin traces (such as 4 or 5 mils) on the PCB will form a large attenuation of the signal, just like a low-pass filter with no attenuation designed, its attenuation increases with frequency. The longer the backplane, the higher the frequency, and the wider the signal line should be. For backplane traces longer than 20 inches, the trace width should be 10 or 12 mils. Usually, the critical signal on the board is the clock signal. When clock lines are too long or poorly designed, they can amplify jitter and skew downstream, especially as speed increases. Multiple layers to transmit the clock should be avoided, and there should be no vias on the clock lines, as vias will increase impedance variations and reflections. If an inner layer must be used to route the clock, then the upper and lower layers should use ground planes to reduce latency. When designing with an FPGA PLL, noise on the power planes can increase PLL jitter. If this is critical, a “power island” can be created for the PLL, which can be used to isolate the PLL analog and digital power supplies using thicker etchings in the metal planes.

For signals with rates above 2Gbps, a more expensive solution must be considered. At such high frequencies, the thickness of the backplane and via design can have a significant impact on signal integrity. Works well when the thickness of the backing plate does not exceed 0.200 inches. When high-speed signals are used on the PCB, the number of layers should be as few as possible to limit the number of vias. In thick boards, the vias connecting the signal layers are longer and will form transmission line branches on the signal path. Using buried vias can solve this problem, but the manufacturing cost is high. Another option is to use a low-loss dielectric material such as Rogers 4350, GETEK, or ARLON. These materials can be nearly double the cost of FR4 materials, but sometimes this is the choice. There are other design techniques for FPGAs that provide some choice of I/O locations. In critical high-speed SERDES designs, SERDES I/Os can be isolated by reserving (but not using) adjacent I/O pins. For example, a 3×3 or 5×5 BGA ball area can be reserved relative to SERDES Rx and Tx, VCCRX# and VCCTX#, and ball position. Or if possible, keep the entire I/O group close to the SERDES. If there are no I/O constraints in the design, these techniques can bring benefits without adding cost. Also one of the ways is to refer to the reference board provided by the FPGA manufacturer. Most manufacturers provide source layout information for reference boards, although special requests may be required due to proprietary information issues. These boards often contain standard high-speed I/O interfaces that FPGA manufacturers need to characterize their devices. Keep in mind, however, that these boards are often designed for multiple purposes and may not necessarily match a specific design need. Nonetheless, they can be used as a starting point for creating solutions.

Summary of this article

Of course, this article only touches on some basic concepts. Any of the topics covered here could be discussed in an entire book. The key is to figure out what the goal is before investing a lot of time and effort into PCB layout design. Once the layout is complete, a redesign can cost a lot of time and money, even with a slight adjustment to the width of the traces. You cannot rely on PCB board layout engineers to make designs that meet actual needs. The schematic designer is always there to provide guidance, make smart choices, and take responsibility for the success of the solution.