1. If you read many PCB board design guides, especially those on parallel protocols and differential pair routing, you will encounter extensive discussion on trace length matching.

2. When trace length matching is necessary, your goal is to minimize the impact of differential pairs in serial protocols and multiple pairs in parallel protocols (e.g., PCIe), as well as multiple traces or pairs in parallel protocols or protocols that use source synchronous clocks.

3. CAD tools simplify the process of analyzing these scenarios. However, what happens at different frequencies? More specifically, what happens with wideband signals?

4. All digital signals are broadband signals, with frequency content extending from DC to infinity. Given the large bandwidth of digital signals, which frequency should be used for trace length matching?

5. Unfortunately, the frequency used for trace length matching is not straightforward, so designers need to understand how to approach PCB trace length matching in relation to frequency.

6. To gain a better understanding, we need to explore the techniques employed in wideband design and how the entire signal bandwidth is accounted for in trace length matching.

1. The relationship between PCB trace length matching and differential pair frequency

2. Properly matching trace length to frequency requires considering the entire signal bandwidth. This has been extensively researched in differential serial protocols, with standards like USB4 imposing specific requirements on wideband signal integrity. Some wideband signal integrity metrics include:

3. Integrated differential crosstalk

4. Integral Differential Insertion Loss

5. Integral Differential Return Loss

6. Integral Differential Impedance Deviation

7. By “integrated,” we mean that a specific aspect of signal integrity applies across the entire frequency range of interest. For example, reducing differential crosstalk between pairs to below a specified limit is crucial. This is key for maintaining length matching accuracy.

8. Dispersion

9. In the time domain, we focus on the transition between HI and LOW states, ensuring both ends of the differential pair align simultaneously. Jitter limits trace length tolerance, preventing perfect transitions. In the frequency domain, consider these dispersions:

10. Geometric dispersion: Influenced by boundary conditions and interconnect geometry, affecting impedance variation.

11. Dielectric dispersion: Occurs in the PCB substrate, independent of interconnect geometry, including dispersion and DK loss.

12. Roughness dispersion: Results from copper roughness and high-frequency skin effects.

13. Fiber weave dispersion: Periodic changes in dispersion due to fiber weave in PCB laminates.

14. These dispersions impact impedance, speed, and signal integrity metrics of PCB traces, making them frequency-dependent.

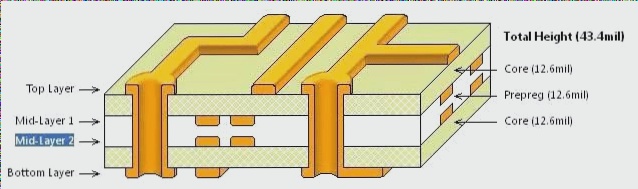

15. Signal speed

16. Transmission line theory links impedance and signal speed. For PCB traces, the figure below illustrates group and phase velocities for a stripline with roughness and dispersion. Phase velocity varies significantly across frequencies, from 1MHz to 20GHz, by a factor of 2. This variability complicates length matching to frequency, necessitating consideration of all frequencies, not just one.

17. Broadband Length Matching vs. Frequency

18. To measure length matching, consider allowable length deviation per signaling standard, termed time bias (tlim). The function k represents the propagation constant, a frequency-dependent dispersion function. A statistical approach, the “Lp norm,” can handle length mismatches. This measure calculates the RMS difference between a function and a constant mean, ideal for addressing variations in design values and signal integrity metrics.

19. Using the Lp norm, we can express allowable length mismatch in terms of an upper bound defined by timing mismatch limit tlim, based on length variation.

20. When applying wideband signal integrity metrics in PCB design, this equation serves as a constraint, affecting the length difference between differential pair ends or any two traces. High-speed parallel protocols are impacted. The integral is straightforward to calculate with the transmission line propagation constant, using field solvers or analytical models. For instance, using simulated stripline phase velocities, a 10ps timing mismatch allows a 1.3041mm length mismatch, a significant fraction of high-speed signal edge rates. Thus, the Lp norm simplifies PCB trace length matching to a single metric, eliminating the need for manual calculations with proper routing tools.

2. When trace length matching is necessary, your goal is to minimize the impact of differential pairs in serial protocols and multiple pairs in parallel protocols (e.g., PCIe), as well as multiple traces or pairs in parallel protocols or protocols that use source synchronous clocks.

3. CAD tools simplify the process of analyzing these scenarios. However, what happens at different frequencies? More specifically, what happens with wideband signals?

4. All digital signals are broadband signals, with frequency content extending from DC to infinity. Given the large bandwidth of digital signals, which frequency should be used for trace length matching?

5. Unfortunately, the frequency used for trace length matching is not straightforward, so designers need to understand how to approach PCB trace length matching in relation to frequency.

6. To gain a better understanding, we need to explore the techniques employed in wideband design and how the entire signal bandwidth is accounted for in trace length matching.

1. The relationship between PCB trace length matching and differential pair frequency

2. Properly matching trace length to frequency requires considering the entire signal bandwidth. This has been extensively researched in differential serial protocols, with standards like USB4 imposing specific requirements on wideband signal integrity. Some wideband signal integrity metrics include:

3. Integrated differential crosstalk

4. Integral Differential Insertion Loss

5. Integral Differential Return Loss

6. Integral Differential Impedance Deviation

7. By “integrated,” we mean that a specific aspect of signal integrity applies across the entire frequency range of interest. For example, reducing differential crosstalk between pairs to below a specified limit is crucial. This is key for maintaining length matching accuracy.

8. Dispersion

9. In the time domain, we focus on the transition between HI and LOW states, ensuring both ends of the differential pair align simultaneously. Jitter limits trace length tolerance, preventing perfect transitions. In the frequency domain, consider these dispersions:

10. Geometric dispersion: Influenced by boundary conditions and interconnect geometry, affecting impedance variation.

11. Dielectric dispersion: Occurs in the PCB substrate, independent of interconnect geometry, including dispersion and DK loss.

12. Roughness dispersion: Results from copper roughness and high-frequency skin effects.

13. Fiber weave dispersion: Periodic changes in dispersion due to fiber weave in PCB laminates.

14. These dispersions impact impedance, speed, and signal integrity metrics of PCB traces, making them frequency-dependent.

15. Signal speed

16. Transmission line theory links impedance and signal speed. For PCB traces, the figure below illustrates group and phase velocities for a stripline with roughness and dispersion. Phase velocity varies significantly across frequencies, from 1MHz to 20GHz, by a factor of 2. This variability complicates length matching to frequency, necessitating consideration of all frequencies, not just one.

17. Broadband Length Matching vs. Frequency

18. To measure length matching, consider allowable length deviation per signaling standard, termed time bias (tlim). The function k represents the propagation constant, a frequency-dependent dispersion function. A statistical approach, the “Lp norm,” can handle length mismatches. This measure calculates the RMS difference between a function and a constant mean, ideal for addressing variations in design values and signal integrity metrics.

19. Using the Lp norm, we can express allowable length mismatch in terms of an upper bound defined by timing mismatch limit tlim, based on length variation.

20. When applying wideband signal integrity metrics in PCB design, this equation serves as a constraint, affecting the length difference between differential pair ends or any two traces. High-speed parallel protocols are impacted. The integral is straightforward to calculate with the transmission line propagation constant, using field solvers or analytical models. For instance, using simulated stripline phase velocities, a 10ps timing mismatch allows a 1.3041mm length mismatch, a significant fraction of high-speed signal edge rates. Thus, the Lp norm simplifies PCB trace length matching to a single metric, eliminating the need for manual calculations with proper routing tools.