Working with Multiple SPI ICs on a Single Bus

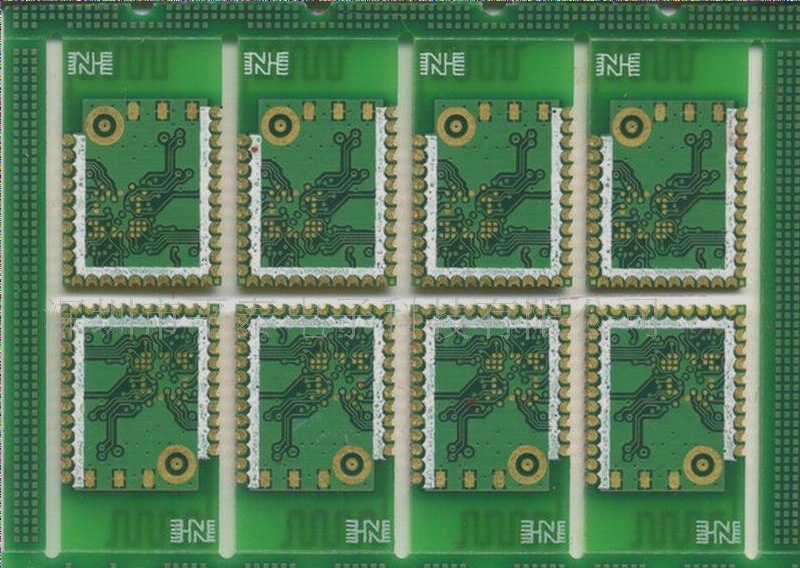

For my current office project, I am dealing with the challenge of incorporating multiple SPI ICs on a single bus. Due to the fixed orientation and pins of the ICs, I had to carefully plan the routing of the bus, as illustrated in the image below.

The bus spans a length of 310 mm, with the signals from the controller inserted in the middle. The SPI clock will be running at a frequency below 10MHz. The PCB is two-sided with a ground flood fill between the layers.

Two main concerns have arisen:

- One concern is the clock line overlapping other signal lines. I am curious about the potential issues this may cause. What are your thoughts on this?

- Another consideration is the length of the bus, specifically 310mm, which means signals have to travel a maximum of 155mm on each side. Are there any other factors I should be mindful of regarding the bus length?

Unfortunately, I am unable to share the complete layout due to the confidential nature of the project. Your insights and advice on these matters would be greatly appreciated.

Thank you.