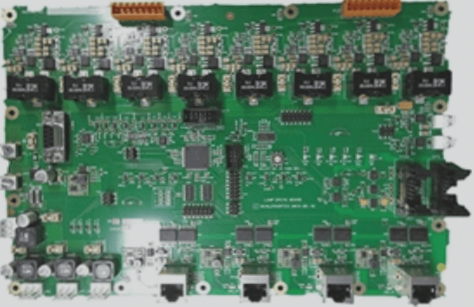

PCB Signal Integrity Challenges

As integrated circuits (ICs) operate at higher switching speeds and PCB densities continue to increase, signal integrity (SI) has become a critical concern in high-speed digital PCB design. Several factors—such as component parameters, PCB board characteristics, component layout, and high-speed signal routing—can contribute to signal integrity issues. These problems can lead to unstable system behavior or even complete system failure.

PCB Signal Integrity Issues: Causes, Effects, and Design Solutions

PCB signal integrity issues are critical to the performance of high-speed digital circuits. These problems primarily include signal reflection, crosstalk, signal delay, and timing errors. Addressing these issues requires an understanding of their causes and the application of best design practices.

1. Reflection

Signal reflection occurs when there is a mismatch between the characteristic impedance of the PCB trace and the source or load impedance. This mismatch results in part of the signal being reflected back toward the source, which distorts the signal waveform. The reflection causes phenomena such as overshoot, undershoot, and ringing.

- Overshoot: Refers to the initial peak (or valley) that exceeds the intended signal level, either above the power rail or below the ground reference.

- Undershoot: Refers to the subsequent dip (or peak) that goes below the reference voltage.

- Ringing: Refers to oscillations that occur as a result of reflections, increasing the time required for the signal to stabilize, thus affecting system timing.

Minimizing reflection requires careful impedance matching between the transmission line, source, and load, as well as the use of termination resistors to dissipate the reflected energy.

2. Crosstalk

Crosstalk refers to unintended interference between signal traces due to electromagnetic coupling. This phenomenon can be capacitive or inductive in nature.

- Capacitive crosstalk: Occurs when mutual capacitance between adjacent traces couples the signal from one trace to another.

- Inductive crosstalk: Occurs when mutual inductance between traces induces unwanted voltage on a neighboring trace.

Crosstalk is influenced by factors such as trace length, signal line spacing, and the quality of the reference ground plane. It is important to manage trace separation and maintain proper grounding to minimize this interference.

3. Signal Delay and Timing Errors

Signal delay is the time it takes for a signal to travel from the driving end to the receiving end of the PCB trace. Excessive delay can lead to timing errors, causing logical errors and malfunctioning of the circuit.

To mitigate these issues, control trace lengths, minimize variations in trace geometry, and ensure clock and data signals are synchronized within design specifications.

4. Design Methods to Ensure Signal Integrity

To optimize signal integrity in PCB design, engineers should consider the following design practices:

(1) Circuit Design Considerations

- Minimize the number of synchronous switching outputs.

Key Strategies for High-Speed PCB Design

- Control the maximum edge rate (dI/dt and dV/dt) of each signal to achieve desired rise and fall times.

- Utilize differential pairs for high-speed signals like clock drivers to mitigate noise interference.

- Place passive components (resistors, capacitors) near transmission line ends for impedance matching.

- Minimize parallel trace lengths to reduce coupling and interference.

- Position sensitive components away from high-speed I/O interfaces to avoid electromagnetic interference.

- Reduce trace-to-reference plane distance to enhance signal integrity.

- Design for lower trace impedance and appropriate signal drive levels to prevent overshoot or undershoot.

- Implement termination resistors or matching networks for load impedance matching.

- Avoid parallel routing and increase spacing between traces to minimize crosstalk.

Latest Insights in High-Speed PCB Design:

Recent advancements in PCB design emphasize the importance of incorporating AI-driven simulations to optimize signal integrity. By leveraging machine learning algorithms, engineers can predict and mitigate signal integrity issues more effectively, leading to enhanced performance and reliability in electronic devices.

Enhancing Signal Integrity Through Simulation:

Simulation tools now offer real-time feedback on signal integrity metrics, allowing designers to make informed decisions during the layout phase. By simulating signal behavior under various conditions, such as temperature fluctuations and voltage changes, designers can proactively address potential signal integrity challenges before prototyping, saving time and resources in the development process.