In order to address the trade-off between manufacturability and product performance in the PCB design process, surface mount device PCB packages are developed in accordance with the IPC-7351b standard.

**Introduction**

Currently, in PCB design, the demands for product miniaturization, high density, and reliability often necessitate compromises between manufacturability and product performance. The package design phase is a critical yet frequently overlooked aspect of PCB design, as its quality has a direct impact on subsequent device assembly and overall product quality. A variety of packaging design standards exist, including international standards, national military standards, corporate standards, and unified design standards, all of which serve as essential guidelines for the design process.

**1. Overview**

**1.1 The Significance of PCB Packaging Design**

During PCB design, certain issues can arise, such as:

1) Mismatches between component specifications and PCB pad dimensions, for instance, using 0603 components on 0805 pads, or vice versa;

2) There are various package designs for components with the same specifications, and the standards lack uniformity;

3) The pad sizes provided by the PCB package do not align with the specification requirements.

These issues stem from inconsistent and non-standardized library construction standards, leading to significant challenges and potential soldering failures during subsequent SMT operations, ultimately impacting product quality and production efficiency. Therefore, PCB packaging design significantly influences the manufacturability and longevity of SMT products.

1.2 Introduction to the IPC-7351b Standard

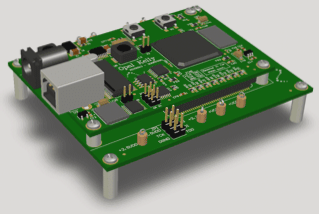

IPC, the International Electronic Industry Connection Association, has established IPC-7351b as a general requirement for surface mount design and land pattern standards, replacing the IPC-SM-782A standard. IPC-7351b recommends designing PCB package pads based on factors such as component density, high-impact environments, and rework requirements. It categorizes PCB packages into three types. As illustrated in Figure 1, users can select the size that best fits their products from these three density options.

1) Density grade A

This grade features maximum pad extension, suitable for low component density applications. Typical examples include portable or handheld products and items subjected to high shock or vibration environments. This structure offers robust soldering and facilitates easy rework when necessary, accommodating both manual and machine soldering with a generous margin.

2) Density class B

This category has medium pad extensions, ideal for products with medium component density, providing a reliable soldering structure. Both manual and machine soldering are feasible.

3) Density class C

This class has the smallest pad extensions, tailored for micro devices with minimal soldering structure requirements on the pad pattern, achieving the highest component assembly density. It is well-suited for machine soldering, though manual soldering is more challenging.

2. Surface Mount Electronic Components Packaging Design

2.1 SMD Pad Design

2.1.1 Calculation of SMD Pad Size for Standard Packages

Standard packages conform to international standards such as JEDEC and EIA, including SOP, SOIC, TSSOP, TQFP, etc. The pad size calculation formula for these package types is as follows:

Where: Z is the distance between the outer edges of the pads on either side of the package; G is the distance between the inner edges of the pads; X is the pad width; L is the distance between the outermost edges of the pins; S is the distance between the inner edges of the pins; W is the pin width; JT is the length of the solder joint extension (toe); JH is the length of the inner edge of the solder joint (heel); JS is the length of the side of the solder joint; CL is the size tolerance of the component (the difference between maximum and minimum L); CS is the size tolerance (the difference between maximum and minimum S); CW is the size tolerance (the difference between maximum and minimum W); F is the tolerance during PCB processing; P is the tolerance during SMT machine soldering.

2.1.2 Pin Calculation Parameters for Various Package Types

The IPC-7351b standard provides recommendations for package calculation parameters JT, JH, and JS for different standard package forms across three density levels, including adjustment coefficients. The packaging parameters can be calculated based on the product’s density grade.

2.1.3 SMD Pad Solder Mask Parameter Setting

The pad solder mask size reflects the opening size of the pad and is generally expanded based on the pad size. The expansion size should be determined according to the manufacturer’s processing capabilities. It is commonly recommended to expand by 6 mils beyond the pad size, and for non-metallized holes, the solder mask size should match the hole size.

2.2.2 Silk Screen Layer

The silk screen layer for the package primarily indicates the physical size range of the device on the PCB and serves as a reference for device positioning during SMT assembly. When designing the SMD device PCB packaging silk screen layer using CADENCE design software, several special considerations must be noted. However, parameters can be adjusted according to production processes.

1) The line width of the silk screen layer is generally set at 5 mils.

2) The outer frame of the silk screen layer should not overlap with the pad, with a distance requirement of ≥10 mils from the pad.

3) The silk screen layer must feature a marking for pin 1 of the device, typically represented by a hollow circle. A recommended line width of 5 mils and a radius of 20 mils facilitate processing and subsequent PCB inspection. The hollow circle should not overlap with other silk screens.

4) For devices with polarity, it is essential to clearly indicate the positive or negative side to assist with assembly and identification.

2.2.3 The Physical Size of the Device

When establishing the PCB package, the package area size can be used as a DRC check item for device layout in CADENCE software. The package area size is typically considered to comprise two elements: the maximum external dimensions of the package and the device pitch required for the soldering process. Table 4 outlines the device spacing needed for common soldering processes. Any interference within the packaging area during PCB design will trigger an automatic error report.

3. Concluding Remarks

In the PCB packaging design process, by comprehensively considering environmental conditions, product performance, density levels, and manufacturability, while adhering to the chip design manual and referencing the IPC-7351 standard, it is indeed possible to design a PCB package that meets product performance requirements with good manufacturability. The author’s organization has implemented density grade A per the IPC-7351b standard to develop a component packaging library, which has significantly enhanced product reliability. Practical results have demonstrated the feasibility of this method, leading to improved weldability and reliability of the products.

**Introduction**

Currently, in PCB design, the demands for product miniaturization, high density, and reliability often necessitate compromises between manufacturability and product performance. The package design phase is a critical yet frequently overlooked aspect of PCB design, as its quality has a direct impact on subsequent device assembly and overall product quality. A variety of packaging design standards exist, including international standards, national military standards, corporate standards, and unified design standards, all of which serve as essential guidelines for the design process.

**1. Overview**

**1.1 The Significance of PCB Packaging Design**

During PCB design, certain issues can arise, such as:

1) Mismatches between component specifications and PCB pad dimensions, for instance, using 0603 components on 0805 pads, or vice versa;

2) There are various package designs for components with the same specifications, and the standards lack uniformity;

3) The pad sizes provided by the PCB package do not align with the specification requirements.

These issues stem from inconsistent and non-standardized library construction standards, leading to significant challenges and potential soldering failures during subsequent SMT operations, ultimately impacting product quality and production efficiency. Therefore, PCB packaging design significantly influences the manufacturability and longevity of SMT products.

1.2 Introduction to the IPC-7351b Standard

IPC, the International Electronic Industry Connection Association, has established IPC-7351b as a general requirement for surface mount design and land pattern standards, replacing the IPC-SM-782A standard. IPC-7351b recommends designing PCB package pads based on factors such as component density, high-impact environments, and rework requirements. It categorizes PCB packages into three types. As illustrated in Figure 1, users can select the size that best fits their products from these three density options.

1) Density grade A

This grade features maximum pad extension, suitable for low component density applications. Typical examples include portable or handheld products and items subjected to high shock or vibration environments. This structure offers robust soldering and facilitates easy rework when necessary, accommodating both manual and machine soldering with a generous margin.

2) Density class B

This category has medium pad extensions, ideal for products with medium component density, providing a reliable soldering structure. Both manual and machine soldering are feasible.

3) Density class C

This class has the smallest pad extensions, tailored for micro devices with minimal soldering structure requirements on the pad pattern, achieving the highest component assembly density. It is well-suited for machine soldering, though manual soldering is more challenging.

2. Surface Mount Electronic Components Packaging Design

2.1 SMD Pad Design

2.1.1 Calculation of SMD Pad Size for Standard Packages

Standard packages conform to international standards such as JEDEC and EIA, including SOP, SOIC, TSSOP, TQFP, etc. The pad size calculation formula for these package types is as follows:

Where: Z is the distance between the outer edges of the pads on either side of the package; G is the distance between the inner edges of the pads; X is the pad width; L is the distance between the outermost edges of the pins; S is the distance between the inner edges of the pins; W is the pin width; JT is the length of the solder joint extension (toe); JH is the length of the inner edge of the solder joint (heel); JS is the length of the side of the solder joint; CL is the size tolerance of the component (the difference between maximum and minimum L); CS is the size tolerance (the difference between maximum and minimum S); CW is the size tolerance (the difference between maximum and minimum W); F is the tolerance during PCB processing; P is the tolerance during SMT machine soldering.

2.1.2 Pin Calculation Parameters for Various Package Types

The IPC-7351b standard provides recommendations for package calculation parameters JT, JH, and JS for different standard package forms across three density levels, including adjustment coefficients. The packaging parameters can be calculated based on the product’s density grade.

2.1.3 SMD Pad Solder Mask Parameter Setting

The pad solder mask size reflects the opening size of the pad and is generally expanded based on the pad size. The expansion size should be determined according to the manufacturer’s processing capabilities. It is commonly recommended to expand by 6 mils beyond the pad size, and for non-metallized holes, the solder mask size should match the hole size.

2.2.2 Silk Screen Layer

The silk screen layer for the package primarily indicates the physical size range of the device on the PCB and serves as a reference for device positioning during SMT assembly. When designing the SMD device PCB packaging silk screen layer using CADENCE design software, several special considerations must be noted. However, parameters can be adjusted according to production processes.

1) The line width of the silk screen layer is generally set at 5 mils.

2) The outer frame of the silk screen layer should not overlap with the pad, with a distance requirement of ≥10 mils from the pad.

3) The silk screen layer must feature a marking for pin 1 of the device, typically represented by a hollow circle. A recommended line width of 5 mils and a radius of 20 mils facilitate processing and subsequent PCB inspection. The hollow circle should not overlap with other silk screens.

4) For devices with polarity, it is essential to clearly indicate the positive or negative side to assist with assembly and identification.

2.2.3 The Physical Size of the Device

When establishing the PCB package, the package area size can be used as a DRC check item for device layout in CADENCE software. The package area size is typically considered to comprise two elements: the maximum external dimensions of the package and the device pitch required for the soldering process. Table 4 outlines the device spacing needed for common soldering processes. Any interference within the packaging area during PCB design will trigger an automatic error report.

3. Concluding Remarks

In the PCB packaging design process, by comprehensively considering environmental conditions, product performance, density levels, and manufacturability, while adhering to the chip design manual and referencing the IPC-7351 standard, it is indeed possible to design a PCB package that meets product performance requirements with good manufacturability. The author’s organization has implemented density grade A per the IPC-7351b standard to develop a component packaging library, which has significantly enhanced product reliability. Practical results have demonstrated the feasibility of this method, leading to improved weldability and reliability of the products.