When analyzing and evaluating the plethora of viewpoints available in articles and on the web, it’s easy to assume that there is a consensus among those well-informed that the days of using conventional low-priced PCB materials for next-generation high-speed layout are over. There is a notion that the demands of modern technologies such as PCIe 5.0 and beyond have pushed the boundaries of board design and manufacture to the edge.

A closer look at the materials and methods involved, however, provides new hope that although we are indeed getting closer to the edge, there are some key changes that we can make, which might enable us to avoid crossing it, at least for the time being.

While it is true that using next-generation materials will allow easier integration of new technologies into designs, this increase in capability and performance comes with a real cost: it is much more expensive to make a PCB using specialty materials. The increase is likely to be in the range of 100% (2×) or even more, depending on the design specifics.

Some companies are more willing to make this transition because their systems and designs can accommodate the use of specialty materials and absorb the additional costs associated with their use. However, there are many others who are subject to tighter design and financial constraints, which would make the transition more challenging.

For this reason, Intel engineers have worked hard to analyze the various factors involved and provide a number of strategies that will allow designers to integrate next-generation technology into their designs using lower cost, current-generation PCB materials and processes.

When integrating next-generation technology into your designs, some increase in manufacturing costs is inevitable. Our research has identified, though, that there are a number of factors that can be controlled to keep the increase to just 30%.

Following are some of the more easily implementable insights that have been obtained from the research that we conducted. As you read, though, it is important to note that this approach is not a cure-all – there are compromises to consider at every level, and while overall cost is important, it is only one of the factors that must be taken into consideration.

Design factors

When manufacturing PCBs, there are any number of factors that need to be considered. However, our efforts have determined that the most benefit comes from focusing on four of these design factors in particular: dielectric material, surface roughness of the copper, oxidation process, and optimization of the stackup. For each design factor, we also list the options that the industry can put efforts into, and provide cost-effective solutions.

1. Dielectric material

Traditional FR4 dielectric materials use an epoxy-based resin with an E-glass support system to keep the cost down. Specialty dielectric materials often require the use of a more expensive PPE/PPO-based resin system and/or low-Dk glass for better performance, increasing the overall manufacturing cost.

Alternative: Newer manufacturing methods have been developed which combine epoxy with the PPE/PPO-based resin, resulting in a finished board with performance characteristics that can meet the performance requirement but at a lower production cost.

2. Surface roughness of copper

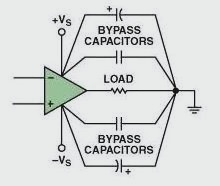

In an ideal scenario, high-speed signals would pass through paths made from copper that have no surface roughness. Unfortunately, in the real world, using ‘smooth’ copper is not a possibility as other materials will have difficulty adhering to it and the PCB will flake and crumble. For boards with higher electrical performance and lower loss requirements, manufacturers use copper with a lower (smoother) profile. The drawback is that these materials are more expensive.

Alternative: Using a newer type of copper foil, commonly referred to as RTF2, is gaining popularity in the industry. RTF2 is a copper foil with a non-uniform roughness profile whose performance is close to high very low profile (HVLP) copper foil but can be manufactured at a lower cost. The next generation of RTF2 copper foil is also being tested to achieve HVLP-like performance with minimal increase in cost.

3. Oxidation process

In PCB production, a surface oxidation process is often required to promote bonding between core and prepreg layers for optimal bonding. A precise balance must be struck during this process because while increasing the surface roughness of copper foil will help to improve bonding, it can have a significant negative impact on the copper profile and thus on signal integrity. An incorrect or unnecessarily aggressive oxidation process can negate the improvements gained by paying for better-performing, lower-profile copper foils by over-roughening them before bonding.

Solution: Low-etch oxidation chemistry and bond promoters – which reduce the need for roughing up of the copper surface while maintaining the desired bonding strength of the PCB – are being developed and adopted by the industry. Less surface oxidation also reduces the potential negative impact on signal integrity, making this approach a win-win.

4. Stackup optimization

In some ways, proper resolution of the PCB stackup is the low-hanging fruit of the performance optimization and cost reduction process because, well, thickness matters.

Solution: When taking a careful look at the signal loss characteristics of the more common core/prepreg layer thickness options, it becomes clear that losses can be minimized simply by taking the time to establish the right stackup. In one test conducted by Intel engineers, it was found that, when measuring signal loss, a 5/6 stackup – 5 mil core thickness and 6 mil prepreg thickness – outperformed a 3/9 stackup by more than 15% using the same substrate and copper profile.

Of course, this approach is not a guarantee, as changes to the stackup can have a negative impact on routing density and noise coupling. However, it does serve to emphasize that careful selection of the stackup and its signal integrity implications are a crucial step in the performance and cost optimization process.

As mentioned above, Intel has undertaken this research initiative as a way to provide alternatives for companies that may find it difficult – or even impossible – to incorporate next-generation materials into their systems and designs. But even with the amount of resources that Intel has, there are gaps in the research and development that we just cannot fill on our own.

So, academia has to be involved in these initiatives at all levels. Many evolutionary advances have been made in this field by industry experts and academicians working together with the common goal of understanding, researching, and addressing the issues that plague PCB manufacturing. This collaborative approach is crucial to ensuring that our industry continues to innovate and grow decades into the future, just as it does today.

A closer look at the materials and methods involved, however, provides new hope that although we are indeed getting closer to the edge, there are some key changes that we can make, which might enable us to avoid crossing it, at least for the time being.

While it is true that using next-generation materials will allow easier integration of new technologies into designs, this increase in capability and performance comes with a real cost: it is much more expensive to make a PCB using specialty materials. The increase is likely to be in the range of 100% (2×) or even more, depending on the design specifics.

Some companies are more willing to make this transition because their systems and designs can accommodate the use of specialty materials and absorb the additional costs associated with their use. However, there are many others who are subject to tighter design and financial constraints, which would make the transition more challenging.

For this reason, Intel engineers have worked hard to analyze the various factors involved and provide a number of strategies that will allow designers to integrate next-generation technology into their designs using lower cost, current-generation PCB materials and processes.

When integrating next-generation technology into your designs, some increase in manufacturing costs is inevitable. Our research has identified, though, that there are a number of factors that can be controlled to keep the increase to just 30%.

Following are some of the more easily implementable insights that have been obtained from the research that we conducted. As you read, though, it is important to note that this approach is not a cure-all – there are compromises to consider at every level, and while overall cost is important, it is only one of the factors that must be taken into consideration.

Design factors

When manufacturing PCBs, there are any number of factors that need to be considered. However, our efforts have determined that the most benefit comes from focusing on four of these design factors in particular: dielectric material, surface roughness of the copper, oxidation process, and optimization of the stackup. For each design factor, we also list the options that the industry can put efforts into, and provide cost-effective solutions.

1. Dielectric material

Traditional FR4 dielectric materials use an epoxy-based resin with an E-glass support system to keep the cost down. Specialty dielectric materials often require the use of a more expensive PPE/PPO-based resin system and/or low-Dk glass for better performance, increasing the overall manufacturing cost.

Alternative: Newer manufacturing methods have been developed which combine epoxy with the PPE/PPO-based resin, resulting in a finished board with performance characteristics that can meet the performance requirement but at a lower production cost.

2. Surface roughness of copper

In an ideal scenario, high-speed signals would pass through paths made from copper that have no surface roughness. Unfortunately, in the real world, using ‘smooth’ copper is not a possibility as other materials will have difficulty adhering to it and the PCB will flake and crumble. For boards with higher electrical performance and lower loss requirements, manufacturers use copper with a lower (smoother) profile. The drawback is that these materials are more expensive.

Alternative: Using a newer type of copper foil, commonly referred to as RTF2, is gaining popularity in the industry. RTF2 is a copper foil with a non-uniform roughness profile whose performance is close to high very low profile (HVLP) copper foil but can be manufactured at a lower cost. The next generation of RTF2 copper foil is also being tested to achieve HVLP-like performance with minimal increase in cost.

3. Oxidation process

In PCB production, a surface oxidation process is often required to promote bonding between core and prepreg layers for optimal bonding. A precise balance must be struck during this process because while increasing the surface roughness of copper foil will help to improve bonding, it can have a significant negative impact on the copper profile and thus on signal integrity. An incorrect or unnecessarily aggressive oxidation process can negate the improvements gained by paying for better-performing, lower-profile copper foils by over-roughening them before bonding.

Solution: Low-etch oxidation chemistry and bond promoters – which reduce the need for roughing up of the copper surface while maintaining the desired bonding strength of the PCB – are being developed and adopted by the industry. Less surface oxidation also reduces the potential negative impact on signal integrity, making this approach a win-win.

4. Stackup optimization

In some ways, proper resolution of the PCB stackup is the low-hanging fruit of the performance optimization and cost reduction process because, well, thickness matters.

Solution: When taking a careful look at the signal loss characteristics of the more common core/prepreg layer thickness options, it becomes clear that losses can be minimized simply by taking the time to establish the right stackup. In one test conducted by Intel engineers, it was found that, when measuring signal loss, a 5/6 stackup – 5 mil core thickness and 6 mil prepreg thickness – outperformed a 3/9 stackup by more than 15% using the same substrate and copper profile.

Of course, this approach is not a guarantee, as changes to the stackup can have a negative impact on routing density and noise coupling. However, it does serve to emphasize that careful selection of the stackup and its signal integrity implications are a crucial step in the performance and cost optimization process.

As mentioned above, Intel has undertaken this research initiative as a way to provide alternatives for companies that may find it difficult – or even impossible – to incorporate next-generation materials into their systems and designs. But even with the amount of resources that Intel has, there are gaps in the research and development that we just cannot fill on our own.

So, academia has to be involved in these initiatives at all levels. Many evolutionary advances have been made in this field by industry experts and academicians working together with the common goal of understanding, researching, and addressing the issues that plague PCB manufacturing. This collaborative approach is crucial to ensuring that our industry continues to innovate and grow decades into the future, just as it does today.