Surface Insulation Resistance (SIR) Measurement in PCBs

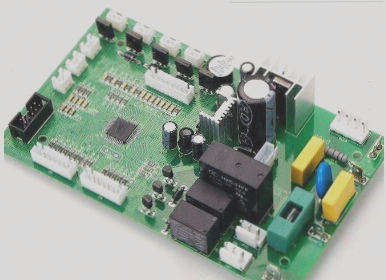

The Surface Insulation Resistance (SIR) test is crucial for evaluating the reliability of printed circuit boards (PCBs). It involves creating a specific electrode pattern on the PCB, applying solder paste, and subjecting the board to controlled high temperature and humidity conditions while applying a bias voltage.

Key Points:

- SIR testing detects short circuits, insulation failures, and leakage between lines over specific time durations (24H, 48H, 96H, 168H).

- It helps identify residues on the PCB surface from flux or other chemicals that may impact electronic component performance.

- SIR testing assesses static surface insulation resistance, dynamic ion migration, and Conductive Anodic Filament (CAF) phenomena related to fiber leakage.

- CAF testing evaluates the impact of flux on moisture absorption and delamination of glass fiber surfaces.

Advantages of SIR Testing:

Surface Insulation Resistance (SIR) testing is effective in evaluating how contaminants affect assembly reliability. It surpasses other methods by detecting both localized and overall pollution effects on PCBs. This method is efficient and practical for assessing PCB reliability.

Additional Information:

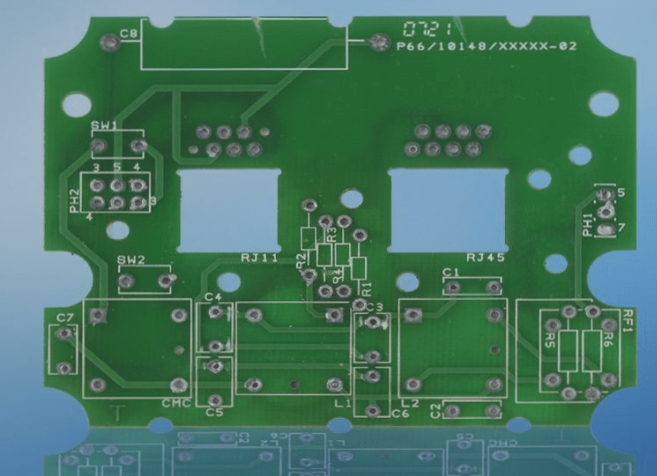

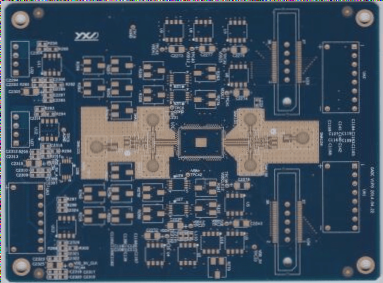

As PCB designs advance with denser layouts and closer solder joints, SIR testing becomes essential for assessing solder paste flux usability. The comb circuit pattern is ideal for high-voltage cleanliness and insulation testing.

Measurement Standards and Process:

- Measurement Standard: IPC-TM-650

- Test Setup: The SIR experiment involves a board with interlaced electrodes forming a comb pattern for testing PCB impedance.

- Testing Conditions: Solder paste is applied to the comb pattern, and the board undergoes testing at 85 ± 2 degrees Celsius with varying humidity levels and bias voltages over specific time intervals.

By following the prescribed testing procedures and recording SIR changes at regular intervals, PCB manufacturers can ensure the reliability and performance of their circuit boards.