Radio frequency (RF) PCB board design is often referred to as a “black art” due to its theoretical uncertainties. However, there are numerous guidelines for RF circuit board design that should not be overlooked. When it comes to the actual design process, the challenge lies in compromising these guidelines and principles to accommodate various design constraints. While there are many important topics in RF design such as impedance matching, insulation materials, laminates, wavelengths, and standing waves, this article will focus on issues related to RF board partition design.

Modern cell phone designs integrate numerous functions in a compact manner, posing challenges for RF board design. The industry is highly competitive, driving the need for integration of multiple functions while minimizing size and cost. Analog, digital, and RF circuits are densely packed with minimal separation, often reducing the number of layers due to cost constraints. Despite the capabilities of multipurpose chips to integrate functions on a small die, the pins connecting to the outside world are closely spaced, leading to proximity of RF, IF, analog, and digital signals that are typically electrically irrelevant.

Designers face challenges with power distribution, as different circuit components are time-shared as needed with software-controlled switching to conserve battery life. This complexity may require multiple working power sources for a cell phone.

RF Layout Concept

When designing an RF layout, several general principles must be prioritized. One such principle is isolating the high-power RF amplifier (HPA) from the low-noise amplifier (LNA) as much as possible. It is essential to keep the high-power RF transmit circuit away from low power RF receive circuits. This may be challenging with limited physical space on the PCB, but there are ways to address this issue.

One approach is to place the high-power and low-power circuits on separate sides of the PCB board or have them work alternately rather than simultaneously. High power circuits may include RF buffers and voltage-controlled oscillators (VCOs). It is crucial to ensure that there is a complete ground in the high-power area on the PCB without vias, as more copper can improve performance.

Later discussions will cover breaking and adapting these design principles as needed. Chip and power supply decoupling are also vital, and various methods for implementing this principle will be expounded upon. Keeping the RF output away from the RF input is necessary, as is isolating sensitive analog signals from high-speed digital and RF signals.

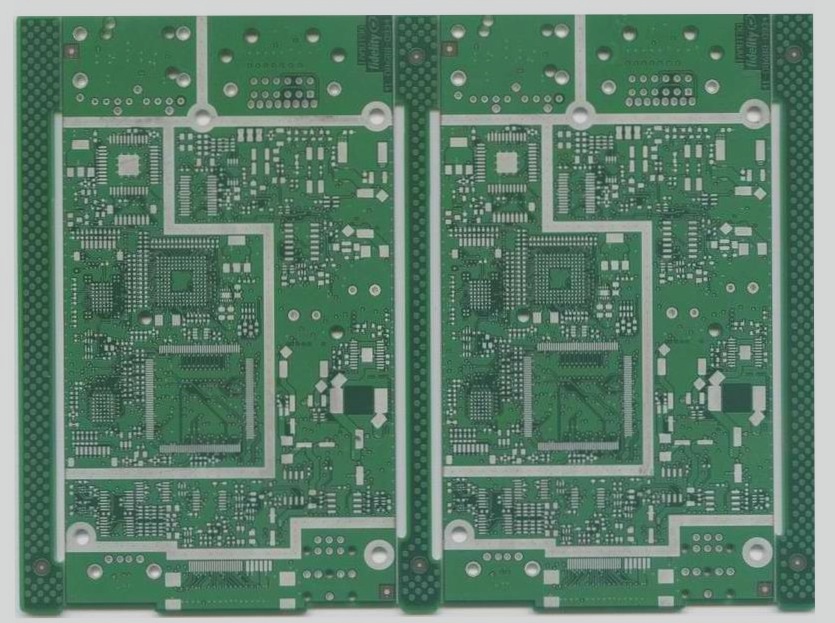

Design partitions can be categorized into physical and electrical partitions. Physical partitions encompass component placement, orientation, and shielding, while electrical partitions focus on power distribution, RF traces, sensitive circuits, and grounding. Effective component placement on the RF path is crucial for successful RF design.

An effective technique involves fixing components along the RF path and adjusting their orientation to minimize RF path length, separate input from output, and isolate high-power circuits from low-power circuits. Board stacking methods can help create dedicated ground planes below the surface layer for improved RF performance. Strategies like reducing via size on the RF path and minimizing straight-through vias can enhance signal integrity.

Metal shields may be required to shield RF energy in the RF area, but they come with their own set of challenges. Ensuring the shielding cover’s integrity and strategically placing decoupling components are critical aspects of successful PCB design. Special attention must be given to decoupling chip power supplies, as inadequate decoupling can lead to signal interference.

Incorporating buffers can help improve isolation and prevent circuit interference. Careful routing of RF signal lines, grounding practices, and component placement are essential for maintaining signal integrity and minimizing noise. While challenges may arise, thorough planning and evaluation in the design stages can prevent costly rework in later stages.

Overall, meticulous attention to detail, adherence to design principles, and strategic component placement are key to successful RF layout design. By implementing these principles, designers can create optimized and efficient RF layouts that meet performance requirements.

Modern cell phone designs integrate numerous functions in a compact manner, posing challenges for RF board design. The industry is highly competitive, driving the need for integration of multiple functions while minimizing size and cost. Analog, digital, and RF circuits are densely packed with minimal separation, often reducing the number of layers due to cost constraints. Despite the capabilities of multipurpose chips to integrate functions on a small die, the pins connecting to the outside world are closely spaced, leading to proximity of RF, IF, analog, and digital signals that are typically electrically irrelevant.

Designers face challenges with power distribution, as different circuit components are time-shared as needed with software-controlled switching to conserve battery life. This complexity may require multiple working power sources for a cell phone.

RF Layout Concept

When designing an RF layout, several general principles must be prioritized. One such principle is isolating the high-power RF amplifier (HPA) from the low-noise amplifier (LNA) as much as possible. It is essential to keep the high-power RF transmit circuit away from low power RF receive circuits. This may be challenging with limited physical space on the PCB, but there are ways to address this issue.

One approach is to place the high-power and low-power circuits on separate sides of the PCB board or have them work alternately rather than simultaneously. High power circuits may include RF buffers and voltage-controlled oscillators (VCOs). It is crucial to ensure that there is a complete ground in the high-power area on the PCB without vias, as more copper can improve performance.

Later discussions will cover breaking and adapting these design principles as needed. Chip and power supply decoupling are also vital, and various methods for implementing this principle will be expounded upon. Keeping the RF output away from the RF input is necessary, as is isolating sensitive analog signals from high-speed digital and RF signals.

Design partitions can be categorized into physical and electrical partitions. Physical partitions encompass component placement, orientation, and shielding, while electrical partitions focus on power distribution, RF traces, sensitive circuits, and grounding. Effective component placement on the RF path is crucial for successful RF design.

An effective technique involves fixing components along the RF path and adjusting their orientation to minimize RF path length, separate input from output, and isolate high-power circuits from low-power circuits. Board stacking methods can help create dedicated ground planes below the surface layer for improved RF performance. Strategies like reducing via size on the RF path and minimizing straight-through vias can enhance signal integrity.

Metal shields may be required to shield RF energy in the RF area, but they come with their own set of challenges. Ensuring the shielding cover’s integrity and strategically placing decoupling components are critical aspects of successful PCB design. Special attention must be given to decoupling chip power supplies, as inadequate decoupling can lead to signal interference.

Incorporating buffers can help improve isolation and prevent circuit interference. Careful routing of RF signal lines, grounding practices, and component placement are essential for maintaining signal integrity and minimizing noise. While challenges may arise, thorough planning and evaluation in the design stages can prevent costly rework in later stages.

Overall, meticulous attention to detail, adherence to design principles, and strategic component placement are key to successful RF layout design. By implementing these principles, designers can create optimized and efficient RF layouts that meet performance requirements.