Reasons for PCB test failures include:

– Damaged chip functions

– Speed/timing discrepancies

– Status of chip pins (floating, high impedance, clock, illegal connections)

– Open collector (OC) lines or statuses

– Fan-out issues

Classification of ICFT test results:

– Test passed

– Test failed

– Device not fully tested

– Devices identical

– Devices compared not identical

(2) How to address different PCB test results

When the “test failed” result appears:

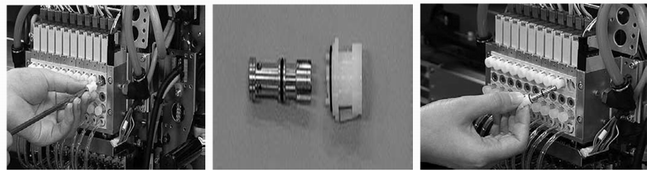

1. Check if the test fixture is correctly connected to the intended chip and ensure proper connection to the tested chip. Verify for any open pins (displaying HIZ) in the pin status window and check the detection of power pins. After correcting these issues, re-test.

2. If the result remains “test failed,” hover over the pin status window with the mouse and left-click to display pin impedance. Compare the impedance of the error-prone pin with another pin serving the same function. In case of a test error on a chip’s output pin, verify if the impedance matches other output pins (considering impedance to ground under powered conditions).

3. If comparable impedances are observed, reduce the test time base or threshold value, and perform the test again. A successful test implies a timing issue with the chip, possibly due to connection with a capacitive device, causing delayed output state due to capacitor discharge. With a passing test post-adjustment, there’s a 90% assurance of the chip’s functionality, allowing progression to test the next chip.

4. If the test continues to fail after adjusting parameters, assess the need for isolation. If isolation isn’t necessary, proceed to step 5.

5. If fixture status indicates failure due to an output pin not reaching normal logic levels, decrease the test threshold and retry. A successful test with lower threshold suggests excessive load on the chip or degraded output drive capability. In such cases, evaluate by re-testing pin impedance under powered and unpowered states on the board under test using the QSM/VI method.

6. Compare impedance measurements of each output pin to ground. Consistent impedance without power and higher impedance on the error-prone pin when powered indicates chip malfunction (inability to manage required current flow). Replace the chip accordingly.

7. Analyze VI curves of each output pin. Significant deviation in impedance on a specific output pin indicates an issue with the connected fan-out load. Identify potential short-circuit points by testing all chip input pins connected to the affected output.

8. To further diagnose, use flat-nose pliers to clamp error-prone output pins on the tested chip and re-test. Successful testing post-clamping indicates load-related issues with the chip.

When the “device not fully tested” result appears:

1. When a tested chip’s output pin fails to toggle during testing (maintaining a constant high or low potential in the test window), the system alerts “device not fully tested” (waveform window remains empty with error marking). For example, if an input pin of a 7400 NAND gate shorts to ground, the corresponding output pin remains high, triggering this prompt.

2. With the PCB schematic diagram of the board under test, users can easily verify normal pin connection status.

3. If using a known good board, compare the learned chip’s normal connection status. For a problematic board, the system automatically compares it with the good board. A match confirms legal connections; proceed without concern over the “device not fully tested” prompt and proceed to test the next chip.

4. For OC devices designed with a “wire-OR” state in the PCB circuit, chip output may be influenced by other chips in a wire-OR relationship. If the input logic of any chip keeps its output at a constant low level, the tested chip’s output will also stay low, triggering the “device not fully tested” prompt. Users should use the QSM/VI method to pinpoint PCB fault points by comparing VI curves of all identical function pins on the test chip.

These modifications aim to enhance clarity and procedural guidance in troubleshooting PCB testing scenarios.