Boundary Scan Test Technology in PCB Boards

Introduction

As products with large-scale integrated circuits become more prevalent, the installation and testing of PCB boards face increasing challenges. Traditional testing methods are struggling to keep up with the miniaturization and packaging of chips, leading to the emergence of new technologies like Boundary Scan Test (BST).

Key Features of BST

- BST adheres to the IEEE1149.1 standard and offers comprehensive testing solutions.

- It eliminates the need for complex test equipment, providing a cost-effective testing approach.

- Benefits include simplicity, reduced test times, and cost savings in production, experimentation, and maintenance.

Basic Composition of BST

The BST circuit follows the IEEE1149.1 standard, comprising the Test Access Port (TAP) with components like the controller, instruction register (IR), and test data register group (TDR).

Test Components:

- Test Access Channel TAP with a 5-pin connector.

- TAP Controller operating as a 16-state state machine.

- Signals like TCK, TMS, TDI, and TDO facilitating test data shifting and control.

Test System for PCB Boards

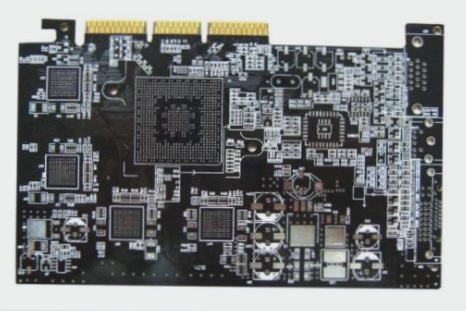

The hardware setup includes a general PC, BST tester, and a serial BST signal cable for connecting to the PCB’s TAP. Each module on the PCB, whether single or multiple chips, must comply with IEEE1149.1 for boundary scan testing.

Test System Structure:

- PCB modules designed with BS registers for boundary scan testing.

- Tester interfaces with PC via a parallel port and with PCB via a serial signal cable.

- Serial signal cables enable flexible testing of chips, modules, or the entire PCB.

Principle of the Test System:

PC software generates test patterns for fault detection based on PCB netlists and device models. Test software includes preprocessors for analysis and execution units for test execution and fault localization.

Test Content:

- Testing PCB I/O pin connectivity for tester access.

- Verifying IC chip integrity through self-tests and internal tests.

Advanced PCB Testing Techniques

- Identification of open circuit and short circuit faults in IC chip interconnections on the PCB, verified through external tests.

- Evaluation of the bus integrity on the PCB to identify open circuit faults on the I/O pins of IC chips linked to the bus.

With the progression of Boundary Scan Test (BST) technology, PCB testing methodologies are constantly evolving, benefiting from the widespread acceptance of programmable integrated circuits. This advancement improves the adaptability and effectiveness of PCB testing procedures while simultaneously reducing the costs associated with test systems. Designers now have the opportunity to utilize programmable logic integrated circuits to develop highly versatile PCBs.