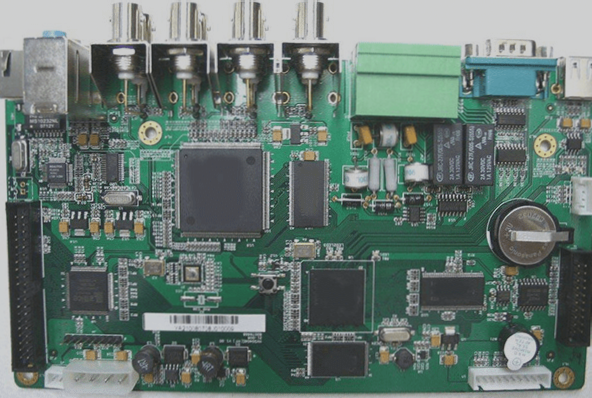

**PCB Design Errors and PCB Quality Acceptance Standards**

**PCB Design Errors**

1. The PCB lacks edges and process holes, which fails to meet the clamping requirements of SMT equipment, rendering it unsuitable for mass production.

2. The PCB shape is irregular, or its dimensions are either too large or too small, making it incompatible with the clamping requirements of the equipment.

3. There are no optical positioning marks (Marks) around the PCB and FQFP pads, or the Mark points do not conform to standards. For instance, the Mark point may have a solder mask around it or be of incorrect size, resulting in insufficient contrast in the Mark point image and frequent machine alarms.

4. The pad structure dimensions are incorrect. For example, if the pad spacing for chip components is either too large or too small, or if the pads are asymmetrical, it can lead to issues such as skew and tombstoning after soldering.

5. Via holes are present on the pads, causing solder to melt and leak through these holes to the bottom layer during soldering, resulting in insufficient solder at the solder joints.

6. The pad sizes for chip components are asymmetric, particularly when the ground wire or other traces are used as pads. This can lead to uneven heating of the pads at both ends of the chip components during reflow soldering, causing the solder paste to melt unevenly and resulting in tombstoning defects.

7. The IC pad design is flawed. The pad in the FQFP is either too wide, leading to bridging after soldering, or the back edge is too short, resulting in insufficient strength post-soldering.

8. The interconnection wires between IC pads are centrally placed, which hampers inspection after SMA welding.

9. The IC lacks auxiliary pads for wave soldering, causing bridging issues post-soldering.

10. Unreasonable PCB thickness or IC placement causes PCB deformation after soldering.

11. The test point design is non-standardized, preventing effective ICT operation.

12. Incorrect spacing between SMDs complicates repair efforts later.

13. The solder mask and character map are not standardized, causing them to overlap pads and leading to virtual soldering or electrical disconnections.

14. Poor board design, such as inadequate processing of V-shaped grooves, results in PCB deformation after reflow.

One or more of these errors may appear in poorly designed products, impacting soldering quality. Designers often lack sufficient knowledge of the SMT process, particularly the “dynamic” component behavior during reflow soldering, contributing to poor design. Additionally, neglecting craftspeople’s input in the early design phase and lacking manufacturability design specifications are also reasons for subpar designs.

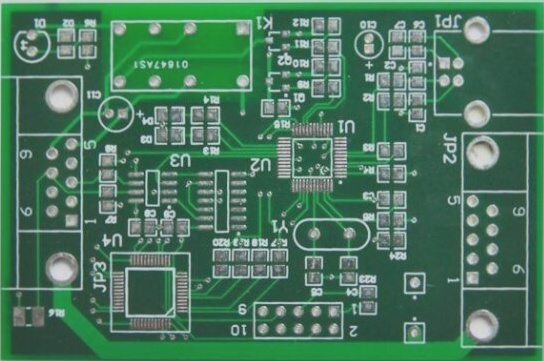

PCB quality acceptance standards encompass design, process, and comprehensive approval. Typically, trial welding, sample sealing, and batch supply precede the following aspects:

1. Electrical connection performance. This is usually self-inspected by the PCB manufacturer using:

– Light board tester (continuity tester) to verify connections and logic relationships, including metallized holes.

– Automatic optical tester for pattern defects to assess comprehensive PCB performance, including lines and characters.

2. Manufacturability. This includes appearance, smoothness, flatness, character cleanliness, via resistivity, electrical properties, heat resistance, solderability, and other comprehensive properties.

– No residual flux, glue, or oily traces on the PCB surface.

– No short circuits or open circuits.

– Non-line conductors (residual copper) must be more than 2.5mm away from lines and the area must be ≤0.25mm².

– Drilling must avoid excessive, missing, or deformed holes and ensure through-hole impermeability.

– No warping of circuits or pads; circuits must not expose copper or tin.

– PCB must not break; VCUT boards must have a depth of at least 1/3 of the board thickness.

– Circuit width deviation from design should be ±20%; shape tolerance is ±0.15mm; substrate edge convexity or unevenness should be ≤0.2mm.

– Solder mask offset should not exceed ±0.15mm; no fingerprints, water lines, or wrinkles on the solder mask surface.

– Component surface text must remain undamaged and recognizable; pad paint coverage should be ≤10% of the original area.

– PCB deformation, bending, and warping should be ≤1% of the substrate’s diagonal length.

After quality acceptance, products are generally vacuum-packed to prevent dust and moisture, extending their storage period. Typically, solderability remains intact for 1 to 2 years of storage.

**PCB Design Errors**

1. The PCB lacks edges and process holes, which fails to meet the clamping requirements of SMT equipment, rendering it unsuitable for mass production.

2. The PCB shape is irregular, or its dimensions are either too large or too small, making it incompatible with the clamping requirements of the equipment.

3. There are no optical positioning marks (Marks) around the PCB and FQFP pads, or the Mark points do not conform to standards. For instance, the Mark point may have a solder mask around it or be of incorrect size, resulting in insufficient contrast in the Mark point image and frequent machine alarms.

4. The pad structure dimensions are incorrect. For example, if the pad spacing for chip components is either too large or too small, or if the pads are asymmetrical, it can lead to issues such as skew and tombstoning after soldering.

5. Via holes are present on the pads, causing solder to melt and leak through these holes to the bottom layer during soldering, resulting in insufficient solder at the solder joints.

6. The pad sizes for chip components are asymmetric, particularly when the ground wire or other traces are used as pads. This can lead to uneven heating of the pads at both ends of the chip components during reflow soldering, causing the solder paste to melt unevenly and resulting in tombstoning defects.

7. The IC pad design is flawed. The pad in the FQFP is either too wide, leading to bridging after soldering, or the back edge is too short, resulting in insufficient strength post-soldering.

8. The interconnection wires between IC pads are centrally placed, which hampers inspection after SMA welding.

9. The IC lacks auxiliary pads for wave soldering, causing bridging issues post-soldering.

10. Unreasonable PCB thickness or IC placement causes PCB deformation after soldering.

11. The test point design is non-standardized, preventing effective ICT operation.

12. Incorrect spacing between SMDs complicates repair efforts later.

13. The solder mask and character map are not standardized, causing them to overlap pads and leading to virtual soldering or electrical disconnections.

14. Poor board design, such as inadequate processing of V-shaped grooves, results in PCB deformation after reflow.

One or more of these errors may appear in poorly designed products, impacting soldering quality. Designers often lack sufficient knowledge of the SMT process, particularly the “dynamic” component behavior during reflow soldering, contributing to poor design. Additionally, neglecting craftspeople’s input in the early design phase and lacking manufacturability design specifications are also reasons for subpar designs.

PCB quality acceptance standards encompass design, process, and comprehensive approval. Typically, trial welding, sample sealing, and batch supply precede the following aspects:

1. Electrical connection performance. This is usually self-inspected by the PCB manufacturer using:

– Light board tester (continuity tester) to verify connections and logic relationships, including metallized holes.

– Automatic optical tester for pattern defects to assess comprehensive PCB performance, including lines and characters.

2. Manufacturability. This includes appearance, smoothness, flatness, character cleanliness, via resistivity, electrical properties, heat resistance, solderability, and other comprehensive properties.

– No residual flux, glue, or oily traces on the PCB surface.

– No short circuits or open circuits.

– Non-line conductors (residual copper) must be more than 2.5mm away from lines and the area must be ≤0.25mm².

– Drilling must avoid excessive, missing, or deformed holes and ensure through-hole impermeability.

– No warping of circuits or pads; circuits must not expose copper or tin.

– PCB must not break; VCUT boards must have a depth of at least 1/3 of the board thickness.

– Circuit width deviation from design should be ±20%; shape tolerance is ±0.15mm; substrate edge convexity or unevenness should be ≤0.2mm.

– Solder mask offset should not exceed ±0.15mm; no fingerprints, water lines, or wrinkles on the solder mask surface.

– Component surface text must remain undamaged and recognizable; pad paint coverage should be ≤10% of the original area.

– PCB deformation, bending, and warping should be ≤1% of the substrate’s diagonal length.

After quality acceptance, products are generally vacuum-packed to prevent dust and moisture, extending their storage period. Typically, solderability remains intact for 1 to 2 years of storage.