PCB Design Guidelines for Ensuring Signal Integrity

Addressing signal integrity (SI) issues early in the PCB design process is crucial for achieving higher design efficiency and avoiding the need for last-minute terminal equipment additions. Here are some key considerations:

- SI Problems: With the increasing switching speeds of IC outputs, almost all designs face SI challenges. Proper grounding and the use of termination devices are essential to maintain design accuracy and prevent critical conditions.

- Simulation and Calculation: SI and EMC experts often run simulations and calculations before routing to adhere to strict design rules and maximize SI safety margins.

- Controlled Impedance Routing: Implementing controlled impedance routing can help mitigate SI issues during the operation of the circuit board.

An ultra-standard design approach is effective in addressing SI issues and ensuring signal integrity throughout the PCB design process.

Common Signal Integrity (SI) Design Guidelines for PCB Fabrication

Pre-design Preparation: Before initiating the design process, it is essential to establish a design strategy that considers component selection, process choices, and cost control. Conducting preliminary research to address SI issues, crosstalk, and timing problems is crucial for a successful design.

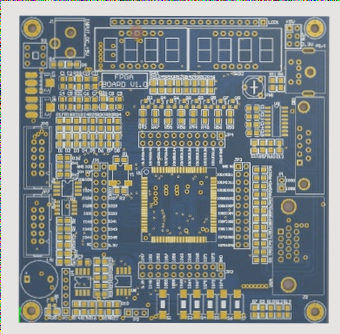

Cascaded Circuit Boards: Understanding project requirements and collaborating with manufacturing engineers is key to determining the number of PCB layers. Impedance control tools should be used to define target impedance ranges, especially for high-speed nodes, to optimize signal integrity.

Collaboration with PCB manufacturers is vital for defining the number of cascades and ensuring the proper arrangement of layers to meet specific thickness requirements. Pairing ground and power planes and utilizing controlled impedance inner layers can help maintain signal integrity and prevent SI problems.

When faced with challenges in defining the return path for signals, simulation tools can aid in predicting the performance of the circuit board.

Crosstalk and Impedance Control

When designing PCBs, it’s crucial to consider the coupling between adjacent signal lines, which can lead to crosstalk and impedance issues. Analyzing the coupling between parallel signal lines helps determine the optimal spacing needed to prevent crosstalk. For instance, maintaining a safe distance between clock and data signals is essential to limit crosstalk while ensuring proper routing.

Key High-speed Node Delays and Timing

High-speed nodes, especially those involved in clock routing, require careful attention to delays and timing. Meeting stringent timing requirements often necessitates specialized equipment for optimal Signal Integrity (SI) performance. Identifying these critical nodes early in the design process and adjusting component placement accordingly is vital for achieving the desired SI.

Choice of PCB Technology and Drive Technology

Choosing the right PCB and drive technologies is essential for different tasks. Factors like signal routing, output requirements, time delays, and noise tolerance play a significant role in SI design. Matching the signal rise time to the appropriate drive technology is key to maintaining good SI quality and addressing issues like simultaneous switching output and electromagnetic compatibility.

Pre-wiring Process

Prior to wiring, defining input parameters for SI analysis and simulating timing and SI results are crucial steps. This information helps establish wiring constraints for PCB layout, ensuring that design guidelines are met. Utilizing software tools for this preparation phase simplifies constraint handling during routing.

Ensuring SI Quality

After assembling the circuit board, testing its performance using tools like oscilloscopes or Time Domain Reflectometers is essential. By comparing actual performance with simulation results, engineers can validate the design’s integrity. Collaboration with IC suppliers is key to obtaining accurate model data for static timing verification, as building precise models can be challenging without reliable sources.