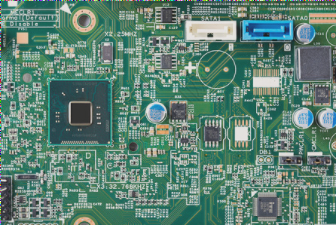

Printed Circuit Boards: The Foundation of Electronic Devices

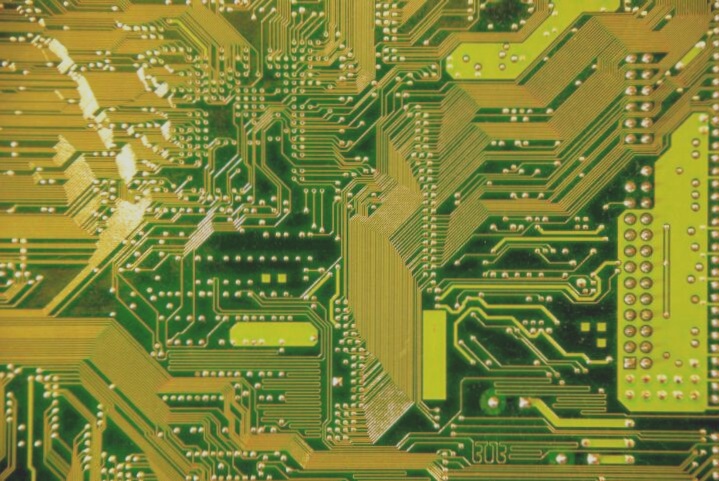

Printed circuit boards (PCBs) are essential components that provide electrical connections between circuit elements in electronic products. As technology advances and components become more densely packed, issues related to electromagnetic compatibility (EMC) are gaining importance.

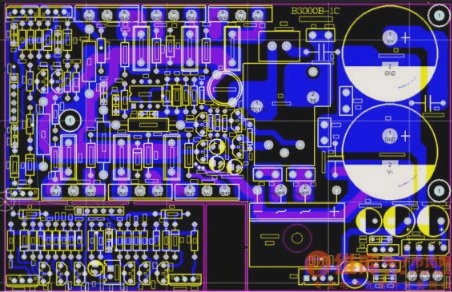

Types of PCBs

- Single-sided and double-sided boards are suitable for low to medium density circuits.

- Multilayer PCBs support high-density circuits and offer solutions for high-speed systems.

Advantages of Multilayer Wiring

- Includes dedicated power and ground layers to minimize interference and impedance issues.

- Specific ground connections for signal traces improve impedance matching and reduce crosstalk.

Laminate Design and Wiring Rules

When designing PCBs, it’s crucial to consider electromagnetic compatibility. Multilayer boards serve as reference planes for high-speed systems, establishing low-impedance current loops for improved EMC performance.

Key Design Considerations

- Choose a reference layer for handling multiple DC voltage regions to prevent interference.

- Position signal layers between reference planes and maintain proper isolation for different signal types.

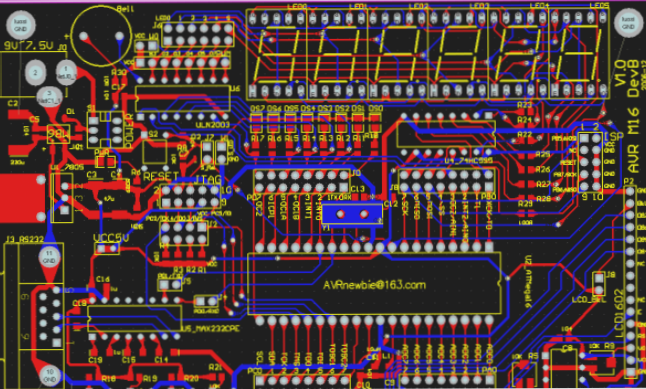

Example Layout of a 12-Layer Board:

The architecture follows the pattern T-P-S-P-S-P-B, with layers numbered 1 through 12. Proper component placement and signal isolation are crucial for reducing interference and ensuring optimal performance.

High-Speed Signal Routing Guidelines for PCB Design

- The fifth, seventh, and ninth layers are designated for high-speed signals. Routing critical signals in a single direction on these layers optimizes routing space. Signal traces between layers should be kept perpendicular to minimize electromagnetic interference. For example, the third and seventh layers can follow east-west routing, while the fifth and ninth layers can be oriented for south-north routing, depending on the signal destination.

- Managing layer transitions during high-speed signal routing is crucial to ensure the return current flows smoothly between reference planes. This minimizes signal loop area and reduces radiation. Pairing specific signal layers (e.g., layers 3, 5, 7, 9) for routing in both orientations can be effective. Avoid pairing layers 3 and 9 to prevent increased loop area.

- Decoupling capacitors’ effectiveness at high frequencies can be compromised by via inductance. Placing decoupling capacitors near vias increases the signal loop area and weakens current radiation.

- Efficient selection of the DC voltage reference layer is essential to address noise generated by high-speed processors. Minimize inductance by keeping traces short, wide, and direct, and using short, thick vias.

- When assigning the second layer as ground and the fourth layer as the processor power supply, keep vias short to minimize distance between the processor and decoupling capacitors. Utilize Table 1 for cascading design layout reference configuration.

- The 20-H Rule and 3-W Rule:

- 20-H Principle: Maintain a distance of at least 20 times the nearest ground plane’s distance (H) from the power plane to reduce RF currents coupling. Adhering to this rule increases the resonant frequency of the PCB.

- 3-W Principle: Ensure spacing between PCB traces is at least three times the trace width (3W) to prevent electromagnetic crosstalk. Trace width is critical for line impedance requirements and signal integrity.