**Understanding and Addressing Unstable Switching Waveforms in Power Supply Design**

A common challenge in switching power supply (SPS) design is the occurrence of “unstable” switching waveforms. This instability can manifest as jitter, particularly in the audio section, where magnetic components might generate unwanted audio noise. Identifying the root cause of such issues can be complex, especially when the problem stems from the PCB layout. Proper layout planning in the early stages of design is therefore critical to achieving optimal performance and minimizing noise-related problems.

To ensure a successful design, power supply engineers must have a comprehensive understanding of both the technical aspects and the functional requirements of the final product. From the very beginning of the project, it’s essential for the power supply designer to collaborate closely with the PCB layout designer. This collaboration should focus on the key electrical layout details that will impact the system’s performance and efficiency.

A well-executed PCB layout offers numerous benefits, such as improved power efficiency, reduced thermal stress, and, most importantly, minimized electromagnetic interference (EMI) and noise. Additionally, a thoughtful layout reduces unwanted interactions between traces and components. Achieving these goals requires the designer to have a clear understanding of current conduction paths and signal flows within the switching power supply. When designing non-isolated switching power supplies, specific design elements must be considered to ensure effective layout and minimize performance issues.

### Key Layout Considerations

1. **Minimizing Interconnection Impedance:**

For embedded DC/DC converters on large PCBs, it’s crucial to position the power output close to the load to reduce trace impedance and conduction losses. This helps in achieving optimal voltage regulation, efficient load transient response, and overall system efficiency. Minimizing trace lengths and optimizing trace widths will ensure that voltage drop and signal distortion are kept to a minimum.

2. **Ensuring Adequate Cooling:**

Thermal stress is a significant factor affecting power supply performance and longevity. To minimize this, proper airflow must be ensured around key components, especially power converters and inductive components. If possible, position the power supply near active cooling components such as fans. This helps to regulate temperature and prevent overheating, which can adversely affect both performance and reliability.

3. **Trace and Component Placement:**

The layout must be designed to reduce the chances of signal interference between traces, particularly high-frequency switching signals. Ensuring proper grounding, using solid ground planes, and maintaining sufficient spacing between high- and low-power traces are critical. In addition, components should be placed in a way that minimizes the loop area for current paths, which can reduce radiated EMI and enhance system stability.

In conclusion, a thorough understanding of both the electrical and thermal requirements, combined with effective collaboration between the power supply and PCB layout engineers, is essential to overcome common issues like unstable switching waveforms. By carefully considering the design elements related to trace impedance, cooling, and component placement, designers can significantly improve power efficiency, reduce thermal stress, and minimize noise interference in switching power supplies.

**Design Considerations for Power Supply and Component Layout in PCB Design**

When designing PCBs, one of the critical aspects is ensuring that large passive components (e.g., inductors and electrolytic capacitors) do not obstruct airflow to low-profile, surface-mounted semiconductor components, such as power MOSFETs or PWM controllers. These components typically require effective thermal management to ensure optimal performance and reliability.

Additionally, to reduce the impact of switching noise on sensitive analog signals, it is essential to avoid routing sensitive signal lines directly beneath power supply traces whenever possible. If this configuration is unavoidable, implementing a dedicated internal ground layer between the power layer and the signal layer can provide crucial shielding against noise.

**1. Early Planning of Power Supply and Board Space**

A successful power supply design begins in the early planning stages, where the power supply’s location and space requirements should be strategically determined. Many designers tend to prioritize other “more exciting” aspects of the circuit, neglecting the power distribution system until later in the design process. This can lead to inefficient layouts and suboptimal power supply designs, which may compromise system reliability and efficiency.

A common mistake is placing power supply components in leftover spaces on the board, disregarding their impact on signal integrity and overall system performance. High-efficiency, reliable power supply design must be treated as a priority, and its placement should be carefully considered from the start.

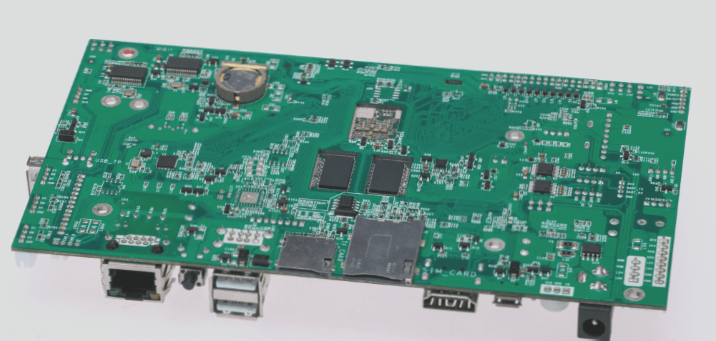

**2. Multilayer PCB Layout Best Practices**

For multilayer PCBs, a common and effective approach is to place a DC ground or DC voltage layer between the high-current power component layer and the sensitive signal trace layer. The ground or voltage plane provides essential AC grounding, effectively shielding small signal traces from interference generated by high-noise power traces or power components.

As a best practice, ensure that the ground and DC voltage planes are not separated. If separation is unavoidable, efforts should be made to minimize trace length and number, and to align trace layouts in the same direction as the high-current path. This reduces the impact of potential interference and voltage drops.

**3. Power Stage Circuit Layout**

The power stage of a switching power supply typically consists of components that handle large currents. These components should be placed first during the layout process, followed by the small-signal control circuitry. This approach ensures that the high-current paths are optimized before the more sensitive signal circuits are placed.

For the high-current traces, it is critical to keep them short and wide to minimize parasitic inductance, resistance, and voltage drops. This is especially important for traces that carry high di/dt pulse currents, which can generate substantial electromagnetic interference (EMI) and voltage spikes.

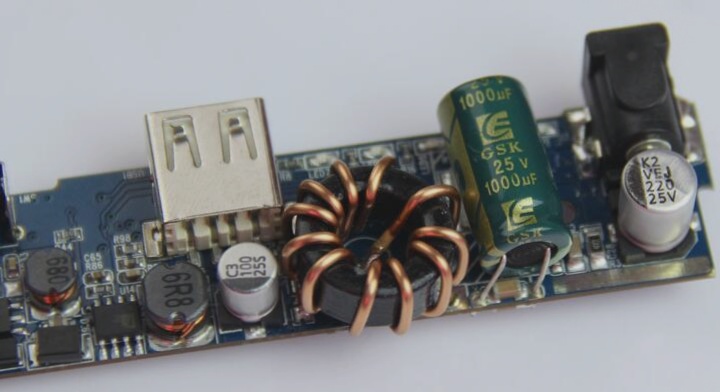

a. **Minimizing Parasitic Inductance**: Parasitic inductance can cause voltage ringing and spikes, especially in high di/dt current paths. To mitigate this, the pulse current loop (often referred to as the thermal loop) should be kept as compact as possible with short, wide traces. This minimizes the loop area and reduces both radiated EMI and voltage transients.

b. **Decoupling Capacitor Selection**: High-frequency decoupling capacitors (CHF) are essential for stabilizing voltage and filtering high-frequency noise. Typically, values between 0.1µF and 10µF with X5R or X7R ceramic dielectrics are recommended. These materials provide low effective series inductance (ESL) and equivalent series resistance (ESR), ensuring effective decoupling performance. Avoid using dielectric materials like Y5V for CHF, as their capacitance can significantly degrade under varying voltage and temperature conditions.

**4. Power Trace Layout in a Buck Converter**

In a buck converter, the layout of the key pulse current loop is vital to system efficiency and stability. To minimize resistance voltage drops and reduce the number of vias, power components should be placed on the same side of the PCB. The high-current power traces should also be routed on the same layer to reduce the path length and impedance. When it is necessary to route a power trace to a different layer, it is important to maintain continuity in the current path to ensure minimal impedance.

Additionally, when using vias to connect high-current loops across layers, it is recommended to use multiple vias. This helps to reduce the overall impedance and maintain efficient current flow, particularly in high-power applications.

By carefully considering these factors in the early stages of PCB design, designers can ensure that both power management and signal integrity are optimized, leading to more efficient, reliable, and high-performance systems.

A common challenge in switching power supply (SPS) design is the occurrence of “unstable” switching waveforms. This instability can manifest as jitter, particularly in the audio section, where magnetic components might generate unwanted audio noise. Identifying the root cause of such issues can be complex, especially when the problem stems from the PCB layout. Proper layout planning in the early stages of design is therefore critical to achieving optimal performance and minimizing noise-related problems.

To ensure a successful design, power supply engineers must have a comprehensive understanding of both the technical aspects and the functional requirements of the final product. From the very beginning of the project, it’s essential for the power supply designer to collaborate closely with the PCB layout designer. This collaboration should focus on the key electrical layout details that will impact the system’s performance and efficiency.

A well-executed PCB layout offers numerous benefits, such as improved power efficiency, reduced thermal stress, and, most importantly, minimized electromagnetic interference (EMI) and noise. Additionally, a thoughtful layout reduces unwanted interactions between traces and components. Achieving these goals requires the designer to have a clear understanding of current conduction paths and signal flows within the switching power supply. When designing non-isolated switching power supplies, specific design elements must be considered to ensure effective layout and minimize performance issues.

### Key Layout Considerations

1. **Minimizing Interconnection Impedance:**

For embedded DC/DC converters on large PCBs, it’s crucial to position the power output close to the load to reduce trace impedance and conduction losses. This helps in achieving optimal voltage regulation, efficient load transient response, and overall system efficiency. Minimizing trace lengths and optimizing trace widths will ensure that voltage drop and signal distortion are kept to a minimum.

2. **Ensuring Adequate Cooling:**

Thermal stress is a significant factor affecting power supply performance and longevity. To minimize this, proper airflow must be ensured around key components, especially power converters and inductive components. If possible, position the power supply near active cooling components such as fans. This helps to regulate temperature and prevent overheating, which can adversely affect both performance and reliability.

3. **Trace and Component Placement:**

The layout must be designed to reduce the chances of signal interference between traces, particularly high-frequency switching signals. Ensuring proper grounding, using solid ground planes, and maintaining sufficient spacing between high- and low-power traces are critical. In addition, components should be placed in a way that minimizes the loop area for current paths, which can reduce radiated EMI and enhance system stability.

In conclusion, a thorough understanding of both the electrical and thermal requirements, combined with effective collaboration between the power supply and PCB layout engineers, is essential to overcome common issues like unstable switching waveforms. By carefully considering the design elements related to trace impedance, cooling, and component placement, designers can significantly improve power efficiency, reduce thermal stress, and minimize noise interference in switching power supplies.

**Design Considerations for Power Supply and Component Layout in PCB Design**

When designing PCBs, one of the critical aspects is ensuring that large passive components (e.g., inductors and electrolytic capacitors) do not obstruct airflow to low-profile, surface-mounted semiconductor components, such as power MOSFETs or PWM controllers. These components typically require effective thermal management to ensure optimal performance and reliability.

Additionally, to reduce the impact of switching noise on sensitive analog signals, it is essential to avoid routing sensitive signal lines directly beneath power supply traces whenever possible. If this configuration is unavoidable, implementing a dedicated internal ground layer between the power layer and the signal layer can provide crucial shielding against noise.

**1. Early Planning of Power Supply and Board Space**

A successful power supply design begins in the early planning stages, where the power supply’s location and space requirements should be strategically determined. Many designers tend to prioritize other “more exciting” aspects of the circuit, neglecting the power distribution system until later in the design process. This can lead to inefficient layouts and suboptimal power supply designs, which may compromise system reliability and efficiency.

A common mistake is placing power supply components in leftover spaces on the board, disregarding their impact on signal integrity and overall system performance. High-efficiency, reliable power supply design must be treated as a priority, and its placement should be carefully considered from the start.

**2. Multilayer PCB Layout Best Practices**

For multilayer PCBs, a common and effective approach is to place a DC ground or DC voltage layer between the high-current power component layer and the sensitive signal trace layer. The ground or voltage plane provides essential AC grounding, effectively shielding small signal traces from interference generated by high-noise power traces or power components.

As a best practice, ensure that the ground and DC voltage planes are not separated. If separation is unavoidable, efforts should be made to minimize trace length and number, and to align trace layouts in the same direction as the high-current path. This reduces the impact of potential interference and voltage drops.

**3. Power Stage Circuit Layout**

The power stage of a switching power supply typically consists of components that handle large currents. These components should be placed first during the layout process, followed by the small-signal control circuitry. This approach ensures that the high-current paths are optimized before the more sensitive signal circuits are placed.

For the high-current traces, it is critical to keep them short and wide to minimize parasitic inductance, resistance, and voltage drops. This is especially important for traces that carry high di/dt pulse currents, which can generate substantial electromagnetic interference (EMI) and voltage spikes.

a. **Minimizing Parasitic Inductance**: Parasitic inductance can cause voltage ringing and spikes, especially in high di/dt current paths. To mitigate this, the pulse current loop (often referred to as the thermal loop) should be kept as compact as possible with short, wide traces. This minimizes the loop area and reduces both radiated EMI and voltage transients.

b. **Decoupling Capacitor Selection**: High-frequency decoupling capacitors (CHF) are essential for stabilizing voltage and filtering high-frequency noise. Typically, values between 0.1µF and 10µF with X5R or X7R ceramic dielectrics are recommended. These materials provide low effective series inductance (ESL) and equivalent series resistance (ESR), ensuring effective decoupling performance. Avoid using dielectric materials like Y5V for CHF, as their capacitance can significantly degrade under varying voltage and temperature conditions.

**4. Power Trace Layout in a Buck Converter**

In a buck converter, the layout of the key pulse current loop is vital to system efficiency and stability. To minimize resistance voltage drops and reduce the number of vias, power components should be placed on the same side of the PCB. The high-current power traces should also be routed on the same layer to reduce the path length and impedance. When it is necessary to route a power trace to a different layer, it is important to maintain continuity in the current path to ensure minimal impedance.

Additionally, when using vias to connect high-current loops across layers, it is recommended to use multiple vias. This helps to reduce the overall impedance and maintain efficient current flow, particularly in high-power applications.

By carefully considering these factors in the early stages of PCB design, designers can ensure that both power management and signal integrity are optimized, leading to more efficient, reliable, and high-performance systems.