1. **Overview**

Today’s computer systems widely employ DDR3 memory technology, with data transmission rates having steadily increased, currently reaching up to 1866 Mbps. Under such high-speed bus conditions, ensuring the reliability of data transmission quality while meeting the timing requirements of the parallel bus presents a significant design challenge. This article focuses on utilizing Cadence’s time-domain analysis tool for a quantitative assessment of DDR3 design. It highlights the key factors influencing signal integrity during DDR3 timing analysis and offers design improvements based on the results to enhance signal quality. These optimizations greatly boost the overall reliability and safety of the system.

2. **Introduction to DDR3**

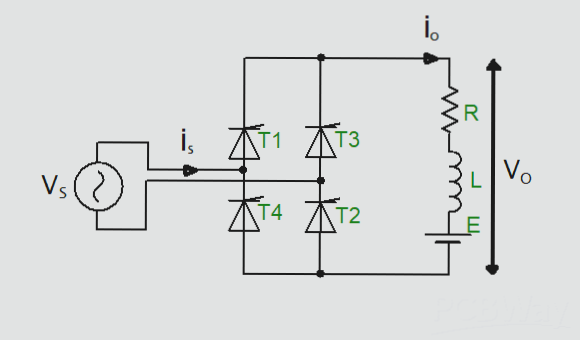

DDR3 memory, similar to DDR2, comprises two main components: controllers and memory modules, both employing source-synchronous timing. This means the selected signal (clock) is not provided by a separate clock source but is generated by the driver chip itself. DDR3 offers a higher data transfer rate than DDR2, with speeds reaching up to 1866 Mbps. It also utilizes 8-bit prefetch technology, significantly enhancing storage bandwidth, and operates at a voltage of 1.5V, reducing power consumption while maintaining the same frequency. DDR3 interface design is challenging due to its use of a unique fly-by topology and advanced techniques like “write equalization” to control internal device offset timing and other measures for optimizing performance.

Although it plays a crucial role in ensuring design implementation and signal integrity, the storage system that supports high frequency and bandwidth is not exhaustive. Therefore, simulation analysis is essential to guarantee both the integrity of the design and the quality of the signal.

3. **Simulation Analysis**

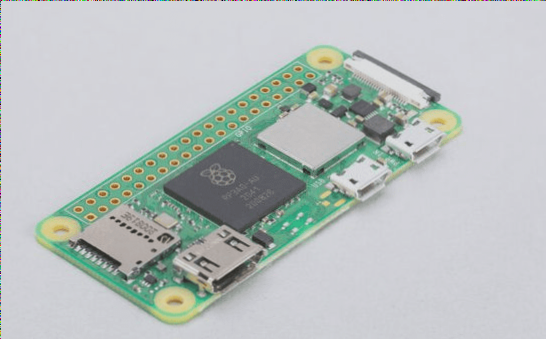

In this section, DDR3 simulation analysis is explained in conjunction with the project. A PowerPC 64-bit dual-core CPU module is chosen, which uses Micron’s MT41J256M16HA-125IT memory.

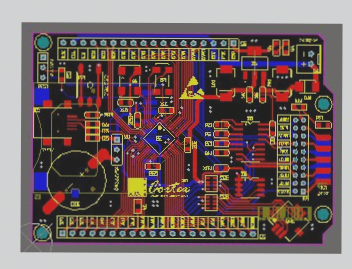

Analyzing the P5020 processor, the module is configured with a memory bus data transfer rate of 1333 MT/s and an analog frequency of 666 MHz.

3.1 **Pre-Simulation Preparation**

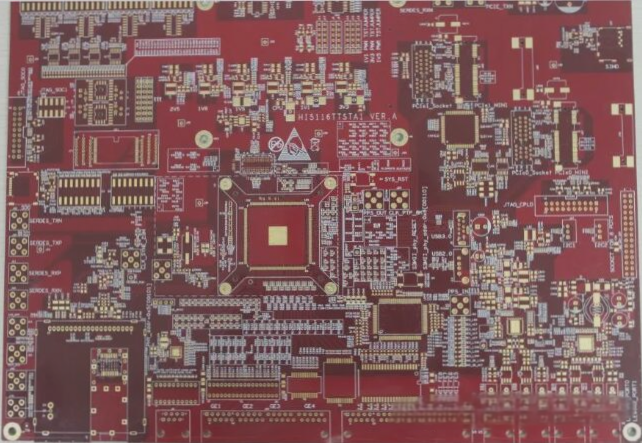

Before beginning the analysis, communication with the PCB manufacturer is required to verify the impedance of DDR3 and confirm its laminated structure. Ensuring the transmission line’s performance in high-speed transmission depends on maintaining consistent characteristic impedance. Impedance control of high-speed PCB signal lines within a specified range is essential, making the printed circuit board a “controllable impedance board,” which forms the basis for analog analysis.

The single-ended impedance of the DDR3 bus is 50Ω, while the differential pair impedance is 100Ω. The voltage values at the analysis network terminals need to be set, along with the passive component model for the analyzed device. The device’s type attributes and pin configurations (input, output, power, ground, etc.) must also be confirmed.

**Solving Signal Integrity in PCB High-Speed Systems**

As data rates increase, signal integrity issues have become one of the most critical factors for design engineers. This rapid growth in data rates is particularly evident in applications like high-bandwidth routers, switches, mobile devices, and consumer display products.

Jitter (noise) is the primary factor that diminishes signal integrity in designs. Beyond utilizing layout optimizations, impedance matching, and higher-quality materials to enhance signal integrity, designers can also add jitter-receiving components such as equalizers to the design to address jitter issues.

By incorporating these techniques, designers can focus more on the core aspects of the system design rather than solely on signal integrity problems. In the past, signal wiring was often considered a simple aspect of the design, with little distinction between video, voice, or data signals. As a result, signal wiring was typically overlooked. However, today’s scenario is vastly different. Video signal transmission speeds now reach 3.3 Gbps per channel, and data signal rates exceed 5 Gbps per channel.

High-speed serial standards such as PCI Express, XAUI, SATA, TMDS, and DisplayPort require design teams and engineers to not only address signal integrity issues but also to understand how these issues affect system performance and reliability. To master this knowledge, engineers must first comprehend the factors that impact signal integrity within the system. Signal integrity degradation is often observable through increased signal jitter. The total jitter in the system comprises two types: random jitter and deterministic jitter. Random jitter is infinite and follows a Gaussian distribution, while deterministic jitter is finite and predictable.

In 90% of systems, deterministic jitter is the primary signal integrity challenge that design engineers must address. Deterministic jitter arises from factors such as inter-symbol interference (ISI), duty cycle distortion, and periodic jitter, which are caused by bandwidth limitations, clock cycle asymmetry, and cross-coupling or EMI issues, respectively.

Passive components such as connectors, PCB traces, and long cables placed along the signal path are significant sources of deterministic jitter. The higher the signal frequency, the greater the attenuation, resulting in a mismatch of power levels within the data stream. This mismatch causes ISI, which reduces signal integrity and can prevent the receiver from correctly interpreting the signal at the receiving end.

The power level mismatch occurs because data can change continuously (0-1-0-1-0-1, etc.) or remain constant (1-1-1-1-1-1, etc.). In the first case, the duty cycle of the alternating data stream is much smaller compared to the constant data stream. As a result, the signal frequency of the varying bits is much higher. If the data stream contains both types, the receiver will experience significantly different power levels for the two signal types, causing issues in signal integrity due to higher frequency attenuation.

**Addressing Power Mismatch**

Most high-speed signal standards require minimizing the number of consecutive bits without changes, such as through 8B/10B encoding. This coding scheme ensures no more than four consecutive bits are the same, helping to maintain signal integrity.

However, it’s still possible for high-power portions of the receiver signal to remain undercompensated. To address this power level mismatch and reduce ISI, PCB designers can apply equalization or de-emphasis techniques.

Equalization boosts the power of high-speed bits, ensuring that both high-speed and low-speed signal components are transmitted with matching power levels, thereby mitigating power mismatch. De-emphasis, conversely, reduces the power of low-speed bits to achieve a similar result: minimizing the power level discrepancy between high-speed and low-speed signals.