With each line edited for clarity and conciseness while preserving the original line count:

1. Each layer in a PCB board serves a specific function in determining electrical behavior.

2. Signal plane layers transmit power and electrical signals between components, but without proper copper plane placement in the internal layers, they may not function correctly.

3. In addition to signal layers, a PCB board requires power and ground planes, which must be correctly positioned in the stack-up to ensure proper operation of the board.

4. So, where should the power, ground, and signal layers be placed? This has long been debated in PCB design, requiring designers to carefully consider the board’s intended application, component functionality, and signal tolerances.

5. Understanding impedance variation limits, jitter, voltage ripple versus PDN impedance, and crosstalk rejection will help you determine the correct arrangement of signal and plane layers.

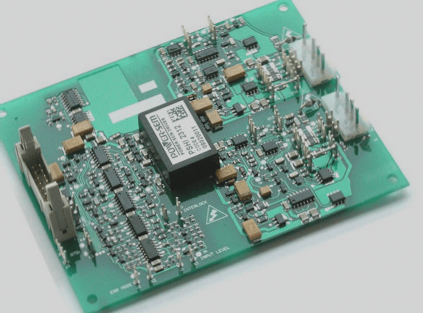

6. Realizing your design intent requires an appropriate PCB design toolset. Whether designing a simple two-layer board or a high-speed PCB with numerous layers, the design software must be suitable for the application.

7. When defining a signal plane stack, entry-level designers might be tempted to take extremes, using either only two layers per board or a dedicated layer for each small stitch.

8. The correct approach lies somewhere in between, depending on the number of nets, acceptable ripple/jitter levels, and the presence of mixed signals.

9. Generally, if a proof of concept functions well on a breadboard, you can use any layout technique on a two-layer board, and it will likely work.

10. For high-speed signals, a grid grounding method might be necessary to provide EMI suppression.

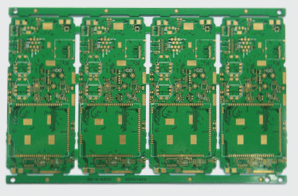

11. For complex devices operating at high speeds or frequencies (or both), you will need at least four PCB stack-up layers: a power plane, a ground plane, and two signal planes.

12. To determine the required number of signal plane layers, first consider the number of signal nets and the approximate width and spacing between them.

13. When estimating the number of signal layers needed in a stack, there are two basic steps you should follow:

**Determining the Net Count:** A simple net count from the schematic and proposed board dimensions can be used to estimate the number of signal layers required. The number of layers is generally proportional to the score, calculated as (net * trace width) / (board width). In other words, more nets with wider traces will necessitate a larger board or more signal layers. Experience should guide the determination of the exact number of signal layers needed to accommodate all nets within the given board size.

**Add Your Plane Layers:** If controlled impedance routing is needed for your signal layers, you must now include reference layers for each controlled impedance signal layer. In cases of densely packed components, a power plane is required beneath the component layer, as there may not be sufficient space on the surface layer to accommodate the power rails. This requirement can lead to a high number of surface layers in HDI boards with a high net value, but the reference layer will offer shielding and maintain consistent characteristic impedance. Once the correct number of layers for a multi-layer board is established, you can proceed to arrange the layers in the PCB board stack-up.

**Designing the PCB Stack-Up:** The next step in PCB stack-up design is to arrange each layer to provide trace paths. Laminates are typically arranged symmetrically around a central core to prevent warping during high-temperature assembly and handling. Proper placement of plane and signal layers is crucial for impedance-controlled routing, as specific equations are needed for different trace placements to ensure impedance control. For rigid-flex stack-up designs, define distinct regions for rigid-flex areas. The layer stack design tool in Allegro simplifies this process. After capturing the schematic as a blank PCB board layout, you can define layer stacks and transitions through different layers. You can then determine the trace size needed for controlled impedance routing.

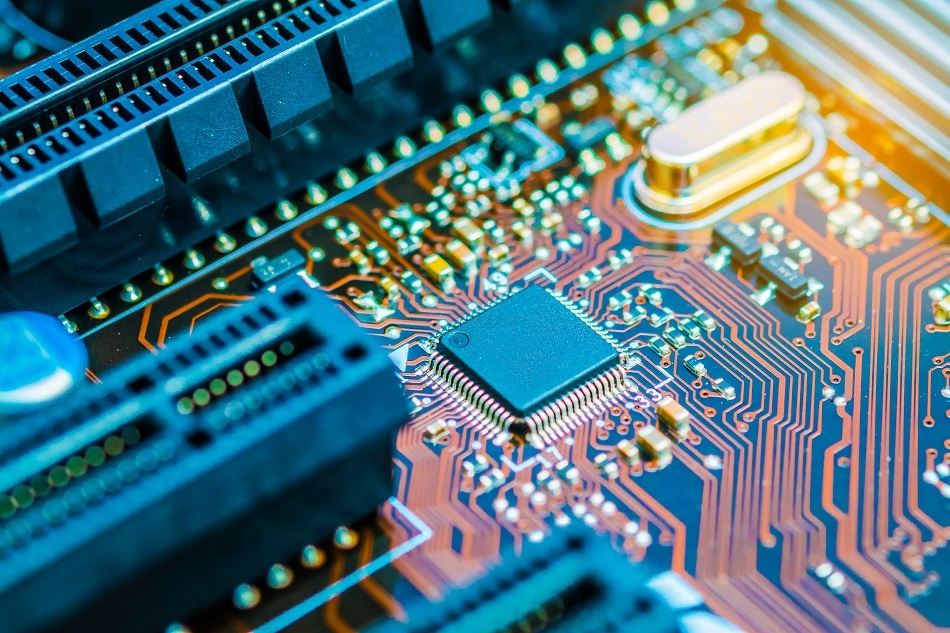

**Stripline vs. Microstrip and Controlled Impedance:** To control impedance, traces routed on inner layers between planar layers should be designed using the stripline impedance equation, which defines the geometry needed for a stripline to achieve a specific characteristic impedance. With three geometric parameters influencing impedance, determining the number of layers required will help establish the layer thickness for a given board thickness. Copper weights for internal signal plane layers are typically 0.5 or 1 oz./sq. ft., using trace width to determine specific characteristic impedance. The same approach applies to microstrip lines on the surface layer. After establishing layer thickness and copper weight, only the trace width needed for the desired characteristic impedance remains to be determined. PCB board design tools include impedance calculators that aid in sizing traces for specific impedance. If differential pairs are used, define the traces as differential pairs, and the impedance calculator will determine the correct trace spacing. When routed on the actual board, traces may be capacitively or inductively coupled to other conductors, potentially altering trace impedance. To ensure impedance targets are met across all layers, use an impedance analysis tool to track impedance throughout the selected signal net. If large impedance variations are detected, adjust traces and routing to correct these changes, with areas of significant impedance variation marked in red. Adjust spacing to eliminate or minimize impedance variation within acceptable tolerances. Define desired impedance tolerance in design rules, and use the post-layout impedance calculator tool to verify routing against this value. The discussion primarily addresses digital signals due to their higher demands compared to analog systems. Analog or mixed-signal boards require a combination of the digital approach described here and an analog-specific approach.

**Bandwidth of Digital vs. Analog Signals:** The bandwidth of a digital signal extends to a certain high frequency, with the corner frequency typically calculated as 0.35/(rise time). For a signal with a rise time of 1 ns, the corner frequency is approximately 350 MHz. For faster digital signals, down to around 20 ps, the knee frequency extends to 17.5 GHz. Analog signals have narrower bandwidths, primarily concerning power plane impedance and insertion/return loss within this bandwidth, making power and signal integrity easier to manage. Losses or high PDN impedance outside this bandwidth are generally negligible.

**Signal Isolation:** A more aggressive option for ensuring isolation between different parts of the board involves using grounded copper pours or through fences. Placing a ground pour next to analog traces creates a coplanar waveguide with high isolation, ideal for high-frequency analog signals. If using fences or other high-frequency conductive isolation structures, employ an electromagnetic field solver to evaluate isolation and decide whether isolation in different signal layers is necessary.

**Return Path:** Mixing analog and digital signals on the board requires careful tracking of ground loop displacement currents and isolation between digital and analog sections. Ensure that analog return paths do not cross near digital components and vice versa. Typically, this involves separating digital and analog signals into different layers with their respective ground planes. Although this increases cost, it ensures effective isolation between different sections. Analog components may also need dedicated analog power strips if drawn from AC power, though this is rare outside of power electronics. Conceptually, it’s manageable as long as return path planning is analyzed. If the analog power section is upstream and separated from the digital section, a single power plane can serve both signals. Correct return path planning can prevent interference between different power and ground sections. For DC power sections with switching regulators, separate the switching noise from the AC section as you would separate digital from analog signals on the PCB.

1. Each layer in a PCB board serves a specific function in determining electrical behavior.

2. Signal plane layers transmit power and electrical signals between components, but without proper copper plane placement in the internal layers, they may not function correctly.

3. In addition to signal layers, a PCB board requires power and ground planes, which must be correctly positioned in the stack-up to ensure proper operation of the board.

4. So, where should the power, ground, and signal layers be placed? This has long been debated in PCB design, requiring designers to carefully consider the board’s intended application, component functionality, and signal tolerances.

5. Understanding impedance variation limits, jitter, voltage ripple versus PDN impedance, and crosstalk rejection will help you determine the correct arrangement of signal and plane layers.

6. Realizing your design intent requires an appropriate PCB design toolset. Whether designing a simple two-layer board or a high-speed PCB with numerous layers, the design software must be suitable for the application.

7. When defining a signal plane stack, entry-level designers might be tempted to take extremes, using either only two layers per board or a dedicated layer for each small stitch.

8. The correct approach lies somewhere in between, depending on the number of nets, acceptable ripple/jitter levels, and the presence of mixed signals.

9. Generally, if a proof of concept functions well on a breadboard, you can use any layout technique on a two-layer board, and it will likely work.

10. For high-speed signals, a grid grounding method might be necessary to provide EMI suppression.

11. For complex devices operating at high speeds or frequencies (or both), you will need at least four PCB stack-up layers: a power plane, a ground plane, and two signal planes.

12. To determine the required number of signal plane layers, first consider the number of signal nets and the approximate width and spacing between them.

13. When estimating the number of signal layers needed in a stack, there are two basic steps you should follow:

**Determining the Net Count:** A simple net count from the schematic and proposed board dimensions can be used to estimate the number of signal layers required. The number of layers is generally proportional to the score, calculated as (net * trace width) / (board width). In other words, more nets with wider traces will necessitate a larger board or more signal layers. Experience should guide the determination of the exact number of signal layers needed to accommodate all nets within the given board size.

**Add Your Plane Layers:** If controlled impedance routing is needed for your signal layers, you must now include reference layers for each controlled impedance signal layer. In cases of densely packed components, a power plane is required beneath the component layer, as there may not be sufficient space on the surface layer to accommodate the power rails. This requirement can lead to a high number of surface layers in HDI boards with a high net value, but the reference layer will offer shielding and maintain consistent characteristic impedance. Once the correct number of layers for a multi-layer board is established, you can proceed to arrange the layers in the PCB board stack-up.

**Designing the PCB Stack-Up:** The next step in PCB stack-up design is to arrange each layer to provide trace paths. Laminates are typically arranged symmetrically around a central core to prevent warping during high-temperature assembly and handling. Proper placement of plane and signal layers is crucial for impedance-controlled routing, as specific equations are needed for different trace placements to ensure impedance control. For rigid-flex stack-up designs, define distinct regions for rigid-flex areas. The layer stack design tool in Allegro simplifies this process. After capturing the schematic as a blank PCB board layout, you can define layer stacks and transitions through different layers. You can then determine the trace size needed for controlled impedance routing.

**Stripline vs. Microstrip and Controlled Impedance:** To control impedance, traces routed on inner layers between planar layers should be designed using the stripline impedance equation, which defines the geometry needed for a stripline to achieve a specific characteristic impedance. With three geometric parameters influencing impedance, determining the number of layers required will help establish the layer thickness for a given board thickness. Copper weights for internal signal plane layers are typically 0.5 or 1 oz./sq. ft., using trace width to determine specific characteristic impedance. The same approach applies to microstrip lines on the surface layer. After establishing layer thickness and copper weight, only the trace width needed for the desired characteristic impedance remains to be determined. PCB board design tools include impedance calculators that aid in sizing traces for specific impedance. If differential pairs are used, define the traces as differential pairs, and the impedance calculator will determine the correct trace spacing. When routed on the actual board, traces may be capacitively or inductively coupled to other conductors, potentially altering trace impedance. To ensure impedance targets are met across all layers, use an impedance analysis tool to track impedance throughout the selected signal net. If large impedance variations are detected, adjust traces and routing to correct these changes, with areas of significant impedance variation marked in red. Adjust spacing to eliminate or minimize impedance variation within acceptable tolerances. Define desired impedance tolerance in design rules, and use the post-layout impedance calculator tool to verify routing against this value. The discussion primarily addresses digital signals due to their higher demands compared to analog systems. Analog or mixed-signal boards require a combination of the digital approach described here and an analog-specific approach.

**Bandwidth of Digital vs. Analog Signals:** The bandwidth of a digital signal extends to a certain high frequency, with the corner frequency typically calculated as 0.35/(rise time). For a signal with a rise time of 1 ns, the corner frequency is approximately 350 MHz. For faster digital signals, down to around 20 ps, the knee frequency extends to 17.5 GHz. Analog signals have narrower bandwidths, primarily concerning power plane impedance and insertion/return loss within this bandwidth, making power and signal integrity easier to manage. Losses or high PDN impedance outside this bandwidth are generally negligible.

**Signal Isolation:** A more aggressive option for ensuring isolation between different parts of the board involves using grounded copper pours or through fences. Placing a ground pour next to analog traces creates a coplanar waveguide with high isolation, ideal for high-frequency analog signals. If using fences or other high-frequency conductive isolation structures, employ an electromagnetic field solver to evaluate isolation and decide whether isolation in different signal layers is necessary.

**Return Path:** Mixing analog and digital signals on the board requires careful tracking of ground loop displacement currents and isolation between digital and analog sections. Ensure that analog return paths do not cross near digital components and vice versa. Typically, this involves separating digital and analog signals into different layers with their respective ground planes. Although this increases cost, it ensures effective isolation between different sections. Analog components may also need dedicated analog power strips if drawn from AC power, though this is rare outside of power electronics. Conceptually, it’s manageable as long as return path planning is analyzed. If the analog power section is upstream and separated from the digital section, a single power plane can serve both signals. Correct return path planning can prevent interference between different power and ground sections. For DC power sections with switching regulators, separate the switching noise from the AC section as you would separate digital from analog signals on the PCB.