1. Increase the distance between the lines to minimize mutual inductance between the interference source and the induced line.

2. PCB Layout and Design: If possible, route the interference source line and the induced line at right angles (or close to right angles) to significantly reduce coupling between them.

3. PCB Layout and Design: Increasing the distance between lines is the most effective method to minimize capacitive coupling.

4. PCB Layout and Design: Before starting the actual routing, classify the wiring based on power levels, grouping them into categories every 30dB.

5. PCB Layout and Design: Different types of wires should be bundled and routed separately. Adjacent wires can be grouped together if shielding or twisting measures are implemented. The minimum distance between classified wiring bundles should be 50 to 75mm.

1. In the resistor layout, the gain control resistors and bias resistors (both up and down) of the amplifier, as well as pull-up and pull-down resistors and regulated rectifier circuits, should be placed as close as possible to the amplifier, active devices, and their power supply and ground. This arrangement helps minimize decoupling effects and improves transient response.

2. Place the bypass capacitor close to the power input.

3. The decoupling capacitor should be positioned as close to each IC as possible, ideally at the power input.

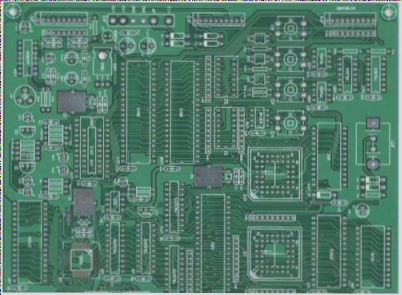

4. Basic PCB characteristics:

– Impedance: Determined by the quality of copper and the cross-sectional area. For 1 ounce copper, the impedance is approximately 0.49 milliohms per unit area.

– Capacitance: ( C = frac{E_0 E_r A}{h} ), where ( E_0 ) is the permittivity of free space, ( E_r ) is the permittivity of the PCB substrate, ( A ) is the area, and ( h ) is the spacing between traces.

– Inductance: Evenly distributed in the wiring, approximately 1 nH/m.

5. For 0.25 mm (10 mil) thick FR4 with 1 ounce copper, a 0.5 mm wide and 20 mm long trace above the ground layer can produce an impedance of 9.8 milliohms, an inductance of 20 nH, and a coupling capacitance to ground of 1.66 pF.

6. Basic principles of PCB layout: Increase trace spacing to reduce capacitive coupling crosstalk; route power and ground lines in parallel to optimize PCB capacitance; keep sensitive high-frequency lines away from high-noise power lines; and widen power and ground wires to lower their impedance.

7. Segmentation: Physically segment different types of signal lines, especially power and ground lines, to reduce coupling between them.

8. Local decoupling: Decouple the local power supply and ICs. Use a large-capacity bypass capacitor between the power input and the PCB to filter low-frequency pulsations and meet burst power requirements. Employ decoupling capacitors between each IC’s power supply and ground, placing these capacitors as close to the IC pins as possible.

9. Wiring separation: Minimize crosstalk and noise coupling between adjacent lines on the same PCB layer. Apply the 3W specification for critical signal paths.

10. Protection and shunt line: Use two-sided grounding protection for key signals and ensure that both ends of the protection line are grounded.

11. Single-layer PCB: The ground wire should be at least 1.5 mm wide, and minimize changes in jumper and ground wire widths.

12. Double-layer PCB: Use ground grid or dot matrix wiring first, maintaining a width of at least 1.5 mm, or place ground on one side and signal power on the other.

13. Protective ring: Form a ring of ground wire to enclose the protective logic for isolation.

14. PCB capacitance: On multilayer boards, PCB capacitance arises from the thin insulating layer between the power supply surface and the ground. This provides high-frequency response and low series inductance uniformly distributed over the board, functioning like a decoupling capacitor spread across the entire surface.

15. High-speed circuits and low-speed circuits: High-speed circuits should be placed close to the ground plane, while low-speed circuits should be near the power plane.

16. Ground copper filling: Ensure that copper filling provides effective grounding.

17. Routing directions: Adjacent layers should have orthogonal routing directions to avoid parallel signal lines on adjacent layers, reducing inter-layer interference. If unavoidable due to board structure limitations (such as certain backplanes), consider using a ground plane to isolate each routing layer and use ground signal lines to isolate each signal line, especially when dealing with high signal rates.

2. PCB Layout and Design: If possible, route the interference source line and the induced line at right angles (or close to right angles) to significantly reduce coupling between them.

3. PCB Layout and Design: Increasing the distance between lines is the most effective method to minimize capacitive coupling.

4. PCB Layout and Design: Before starting the actual routing, classify the wiring based on power levels, grouping them into categories every 30dB.

5. PCB Layout and Design: Different types of wires should be bundled and routed separately. Adjacent wires can be grouped together if shielding or twisting measures are implemented. The minimum distance between classified wiring bundles should be 50 to 75mm.

1. In the resistor layout, the gain control resistors and bias resistors (both up and down) of the amplifier, as well as pull-up and pull-down resistors and regulated rectifier circuits, should be placed as close as possible to the amplifier, active devices, and their power supply and ground. This arrangement helps minimize decoupling effects and improves transient response.

2. Place the bypass capacitor close to the power input.

3. The decoupling capacitor should be positioned as close to each IC as possible, ideally at the power input.

4. Basic PCB characteristics:

– Impedance: Determined by the quality of copper and the cross-sectional area. For 1 ounce copper, the impedance is approximately 0.49 milliohms per unit area.

– Capacitance: ( C = frac{E_0 E_r A}{h} ), where ( E_0 ) is the permittivity of free space, ( E_r ) is the permittivity of the PCB substrate, ( A ) is the area, and ( h ) is the spacing between traces.

– Inductance: Evenly distributed in the wiring, approximately 1 nH/m.

5. For 0.25 mm (10 mil) thick FR4 with 1 ounce copper, a 0.5 mm wide and 20 mm long trace above the ground layer can produce an impedance of 9.8 milliohms, an inductance of 20 nH, and a coupling capacitance to ground of 1.66 pF.

6. Basic principles of PCB layout: Increase trace spacing to reduce capacitive coupling crosstalk; route power and ground lines in parallel to optimize PCB capacitance; keep sensitive high-frequency lines away from high-noise power lines; and widen power and ground wires to lower their impedance.

7. Segmentation: Physically segment different types of signal lines, especially power and ground lines, to reduce coupling between them.

8. Local decoupling: Decouple the local power supply and ICs. Use a large-capacity bypass capacitor between the power input and the PCB to filter low-frequency pulsations and meet burst power requirements. Employ decoupling capacitors between each IC’s power supply and ground, placing these capacitors as close to the IC pins as possible.

9. Wiring separation: Minimize crosstalk and noise coupling between adjacent lines on the same PCB layer. Apply the 3W specification for critical signal paths.

10. Protection and shunt line: Use two-sided grounding protection for key signals and ensure that both ends of the protection line are grounded.

11. Single-layer PCB: The ground wire should be at least 1.5 mm wide, and minimize changes in jumper and ground wire widths.

12. Double-layer PCB: Use ground grid or dot matrix wiring first, maintaining a width of at least 1.5 mm, or place ground on one side and signal power on the other.

13. Protective ring: Form a ring of ground wire to enclose the protective logic for isolation.

14. PCB capacitance: On multilayer boards, PCB capacitance arises from the thin insulating layer between the power supply surface and the ground. This provides high-frequency response and low series inductance uniformly distributed over the board, functioning like a decoupling capacitor spread across the entire surface.

15. High-speed circuits and low-speed circuits: High-speed circuits should be placed close to the ground plane, while low-speed circuits should be near the power plane.

16. Ground copper filling: Ensure that copper filling provides effective grounding.

17. Routing directions: Adjacent layers should have orthogonal routing directions to avoid parallel signal lines on adjacent layers, reducing inter-layer interference. If unavoidable due to board structure limitations (such as certain backplanes), consider using a ground plane to isolate each routing layer and use ground signal lines to isolate each signal line, especially when dealing with high signal rates.