1. Vias, also known as metallized holes, are essential in double-sided and multilayer PCBs.

2. To connect the traces or planes of the same network across different layers, a via must be drilled at the intersection of traces or copper foil planes between layers. The hole is then plated with copper through electroplating, allowing electrical connection between layers. These metalized vias are crucial for enabling inter-layer connectivity.

3. Unlike the pads of through-hole components, vias do not have a soldering layer. Typically, the via pads are covered with insulating ink.

4. However, some manufacturers with less refined processes may leave via pads exposed. In these cases, when components are soldered, especially on automated SMT lines, impurities such as solder balls may adhere to the via pads, potentially causing short circuits.

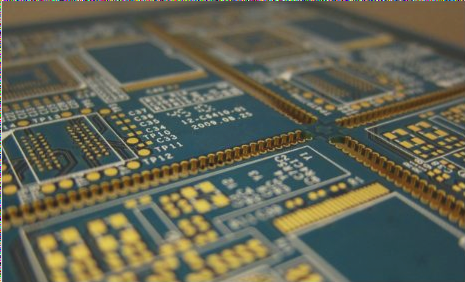

5. In multilayer PCBs, vias can be through holes, blind holes, or buried holes.

6. Through vias extend through all the layers of the circuit board and can connect traces across all electrical layers.

7. Blind vias connect traces from the surface to inner layers. They are visible from one side but not from the other.

8. Buried vias, on the other hand, connect traces between inner layers. These are called “buried” vias because they are concealed within the PCB and cannot be seen on the surface.

9. Through vias are typically mechanically drilled, blind vias are usually drilled on pads and are smaller in size, often created using laser drilling, while buried vias can involve both types of drilling methods.

10. **Note:** The design of blind and buried vias in multilayer boards must consider the PCB manufacturing process and lamination structure. Depending on the number of layers involved, blind and buried vias are classified into first-order, second-order, or multi-stage vias. The more stages there are, the more complex the manufacturing process becomes, resulting in higher costs. Therefore, if your design requires blind or buried vias, it’s essential to consult with the manufacturer to ensure that an appropriate lamination structure is selected before beginning the design.

11. The main parameters for a via are the inner diameter (the size of the hole), the outer diameter (the size of the pad), and the copper thickness of the via wall (the thickness of the electroplated copper inside the hole).

12. So, how do we select the right parameters for drilling the via holes, such as hole size and copper foil thickness?

13. New layout engineers might think that the via parameters should simply match the process capabilities of the PCB manufacturer. For instance, a common search on the internet might suggest that the minimum mechanical via size is 0.2mm, so they may choose 0.2mm for the via size.

14. At first glance, this seems reasonable. However, from another perspective, it’s important to remember a fundamental rule of PCB layout: traces should always be as short as possible. Does your design strictly adhere to this principle?

15. If the traces aren’t the shortest, why should the vias be the smallest?

The industry’s process capability can achieve a minimum aperture of 0.2mm, but several limitations exist. For instance, if the board thickness is less than 1.0mm, your board may require a thickness of 1.6mm or even 2.0mm to accommodate a 0.2mm aperture. Under such conditions, production can lead to damage and significant wear on the CNC drill bit, resulting in a low yield rate and potentially doubling manufacturing costs due to the small via size, or even rendering production impossible.

Even if your board thickness meets the requirements, let’s consider the reality of the production line. The PCB manufacturing process includes material preparation, drilling, and multiple steps like conductive film coating and electroplating to ensure uniform copper foil distribution within the hole.

If you choose a via with an inner diameter of 0.2mm, the manufacturing process requires that the conductive film and electroplated copper occupy some of the space. Therefore, to achieve a finished hole diameter of 0.2mm, a CNC drill bit larger than 0.2mm must be used—typically a 0.25mm bit— to achieve the desired hole size.

If the board density is high, with traces or copper foil around the vias, and their spacing is smaller than the CNC drill bit size, the manufacturer will need to make adjustments to your Gerber files in order to drill the hole. A responsible manufacturer will modify the surrounding traces, while an irresponsible one might cut the copper directly, potentially altering your carefully designed routing, trace width, and spacing. The result is a board that fails to meet the design requirements, and hardware debugging will not align with the original design intent.

In the end, a variety of unforeseen issues may arise in the product, and you might not realize that all of this stems from a seemingly insignificant parameter choice. Is this the legendary butterfly effect?

PCB layout isn’t just hard work; hardware engineers may be forced into becoming reluctant philosophers.

Therefore, to ensure high yield and low-cost PCB products, when setting PCB layout parameters, avoid pushing the limits of the manufacturing process. As for technological advances and societal development, let the equipment manufacturers handle the related tasks. Our goal is to ensure that the final product meets the design specifications during manufacturing.

So, how should we set via parameters?

First, consult with your supplier. The manufacturer will provide appropriate suggestions, and you should add 0.1–0.2mm to the aperture size based on their recommendation to avoid future cost reductions due to process restrictions or supplier limitations.

Second, for boards with high PCB density, consider increasing the number of layers. A well-thought-out increase in layers and layout can enhance the product’s electromagnetic compatibility (EMC).

Third, for POWER and GND vias that will carry large currents, increase the via size by 0.1–0.2mm (mainly to increase the copper foil area of the via, which is akin to widening the via traces) and use multiple vias for connections.