QFN (Quad Flat No-leads) packaging has become increasingly popular in the PCB industry for IC packaging. QFN offers several advantages, such as a small form factor, similar to Chip Scale Packaging (CSP), and relatively low cost. The yield rate in IC production is also quite high, and the package provides superior coplanarity and heat dissipation, making it ideal for high-speed and power management circuits. Additionally, the QFN package does not require leads on all four sides, which enhances its electrical efficiency compared to traditional leaded packages. In contrast, traditional PCB-mounted ICs, such as SO packages with multiple pins, must route leads from the sides.

Despite the numerous electrical and application benefits of QFN packaging, it introduces challenges related to soldering quality in PCB assembly. Due to the leadless design, it is often difficult to assess the solderability by inspecting the appearance of the solder joints. Although some solder joints are visible on the sides of the QFN package, certain IC manufacturers only trim the lead frame to expose the sides, and this cut area does not require electroplating. As a result, it is typically challenging to achieve proper soldering on the sides of the QFN package. Moreover, the cut sections are prone to oxidation over time, making it even more difficult for the tin to adhere to the side, further complicating the soldering process.

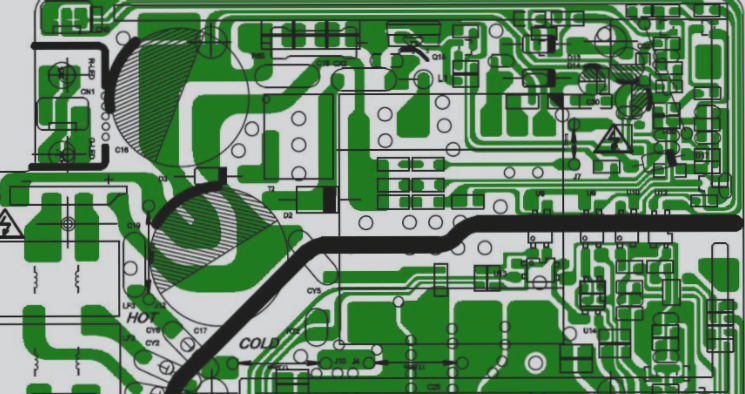

▼ The side solder foot of a QFN is the cut portion of the lead frame that lacks electroplating coating.

**QFN Tin Standard**

In fact, section 8.2.13 of the IPC-A-610D specification does not explicitly state that the side tin of a QFN must have a smooth, curved arc. The Plastic Quad Flat No-lead (PQFN) package does not mandate a specific side tin design.

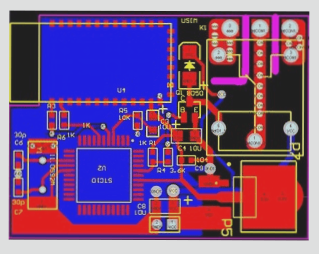

Some package configurations do not expose solder toes, or the exposed solder toes on the outside of the package lack a continuous solderable surface, which means no toe fillet is formed. In other words, QFN soldering cannot follow the same conditions as side pipe soldering. The main requirement is that the bottom of the QFN solder leg, along with the area near the heat sink at the bottom-right corner, must have adequate tinning. The tinning of the QFN bottom solder feet can be viewed similarly to BGA soldering. Thus, it is recommended to refer to the plastic BGA standards in section 8.2.12 of IPC-A-610D. The amount of tin plating on the middle ground pad may vary depending on the design specifications of each PCB manufacturer.

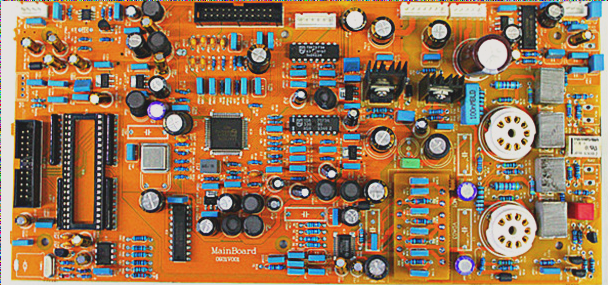

▼ While the solder pins on the QFN side may not be ideal for tin attraction, the bottom surface of these pins has good tin absorption, and their electrical performance remains satisfactory.

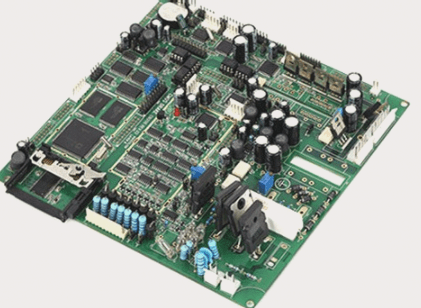

▼ The solder feet on the side of the QFN are typically in good condition.

QFN solderability inspection and testing follow the same standards as those for BGA soldering. Currently, QFN solder inspection utilizes in-circuit testing and functional verification to assess performance. Additionally, optical inspection or X-ray inspection is used to detect open or short circuits in the solder joints. To be honest, if the X-ray system resolution is insufficient, detecting QFN soldering defects can be quite challenging. If solderability issues are found, they can only be confirmed through destructive testing (such as cross-sectioning or red dye penetration tests).

**Possible Solutions for QFN Soldering Issues**

If open solder joints are detected on the QFN, it’s important to first determine if oxidation is the cause. A tin immersion test can help confirm whether there are solder joint issues. Generally, ground pins are more susceptible to open solder joints. You may consider modifying the PCB layout by adding heat dissipation pads to the traces, thereby reducing the number of ground pins. This will slow down the heat dissipation (the term “thermal resistance” refers to reducing the width of the ground trace so that heat is not quickly transmitted to the entire ground plane). Additionally, adjusting the furnace temperature (reflow profile) or switching to a slope reflow type can help reduce the excessive heat absorption by the solder paste during preheating.

**Reference Reading: Reflow Curve**

It has been observed that excessive solder paste on the ground pad of the QFN can cause the component to float during reflow soldering, leading to an open solder joint. In such cases, it’s better to print solder paste only on the ground pad beneath the QFN, rather than printing it across the entire pad. Since the solder paste will melt into balls during reflow, the component is less likely to float.

**Reference Reading: Through-hole Processing in Pads**

Furthermore, it is advisable to avoid placing through-holes in the PCB pads and to block any through-holes in the central heat dissipation ground pad. If through-holes are left unblocked, they can affect the amount of solder and potentially generate bubbles, leading to poor solder joints in severe cases.

If your have any questions about PCB ,please contact me info@wellcircuits.com

Despite the numerous electrical and application benefits of QFN packaging, it introduces challenges related to soldering quality in PCB assembly. Due to the leadless design, it is often difficult to assess the solderability by inspecting the appearance of the solder joints. Although some solder joints are visible on the sides of the QFN package, certain IC manufacturers only trim the lead frame to expose the sides, and this cut area does not require electroplating. As a result, it is typically challenging to achieve proper soldering on the sides of the QFN package. Moreover, the cut sections are prone to oxidation over time, making it even more difficult for the tin to adhere to the side, further complicating the soldering process.

▼ The side solder foot of a QFN is the cut portion of the lead frame that lacks electroplating coating.

**QFN Tin Standard**

In fact, section 8.2.13 of the IPC-A-610D specification does not explicitly state that the side tin of a QFN must have a smooth, curved arc. The Plastic Quad Flat No-lead (PQFN) package does not mandate a specific side tin design.

Some package configurations do not expose solder toes, or the exposed solder toes on the outside of the package lack a continuous solderable surface, which means no toe fillet is formed. In other words, QFN soldering cannot follow the same conditions as side pipe soldering. The main requirement is that the bottom of the QFN solder leg, along with the area near the heat sink at the bottom-right corner, must have adequate tinning. The tinning of the QFN bottom solder feet can be viewed similarly to BGA soldering. Thus, it is recommended to refer to the plastic BGA standards in section 8.2.12 of IPC-A-610D. The amount of tin plating on the middle ground pad may vary depending on the design specifications of each PCB manufacturer.

▼ While the solder pins on the QFN side may not be ideal for tin attraction, the bottom surface of these pins has good tin absorption, and their electrical performance remains satisfactory.

▼ The solder feet on the side of the QFN are typically in good condition.

QFN solderability inspection and testing follow the same standards as those for BGA soldering. Currently, QFN solder inspection utilizes in-circuit testing and functional verification to assess performance. Additionally, optical inspection or X-ray inspection is used to detect open or short circuits in the solder joints. To be honest, if the X-ray system resolution is insufficient, detecting QFN soldering defects can be quite challenging. If solderability issues are found, they can only be confirmed through destructive testing (such as cross-sectioning or red dye penetration tests).

**Possible Solutions for QFN Soldering Issues**

If open solder joints are detected on the QFN, it’s important to first determine if oxidation is the cause. A tin immersion test can help confirm whether there are solder joint issues. Generally, ground pins are more susceptible to open solder joints. You may consider modifying the PCB layout by adding heat dissipation pads to the traces, thereby reducing the number of ground pins. This will slow down the heat dissipation (the term “thermal resistance” refers to reducing the width of the ground trace so that heat is not quickly transmitted to the entire ground plane). Additionally, adjusting the furnace temperature (reflow profile) or switching to a slope reflow type can help reduce the excessive heat absorption by the solder paste during preheating.

**Reference Reading: Reflow Curve**

It has been observed that excessive solder paste on the ground pad of the QFN can cause the component to float during reflow soldering, leading to an open solder joint. In such cases, it’s better to print solder paste only on the ground pad beneath the QFN, rather than printing it across the entire pad. Since the solder paste will melt into balls during reflow, the component is less likely to float.

**Reference Reading: Through-hole Processing in Pads**

Furthermore, it is advisable to avoid placing through-holes in the PCB pads and to block any through-holes in the central heat dissipation ground pad. If through-holes are left unblocked, they can affect the amount of solder and potentially generate bubbles, leading to poor solder joints in severe cases.

If your have any questions about PCB ,please contact me info@wellcircuits.com