PCB Design Tips for RF Circuits

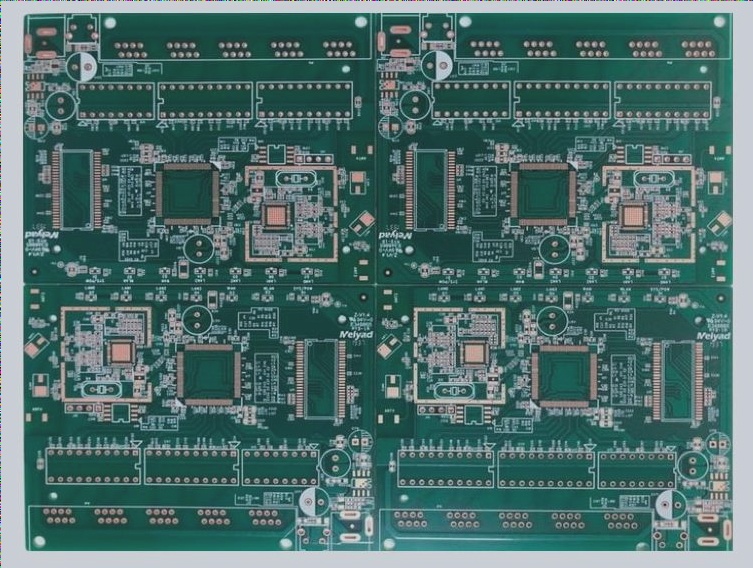

- Utilize low-cost PCBs for quick prototyping using various CAD software.

- Consider 50Ω traces for RF circuits for optimal performance.

- CPWG structures help create smaller RF traces on PCBs.

- Adding a copper ground plane can adjust impedance to 50Ω.

- Use 3-D electromagnetic simulators for accurate CPWG design.

- Ensure proper spacing and trace width for impedance control.

- Include vias for high-frequency performance and signal integrity.

Modern PCB design requires attention to detail, especially for RF circuits. By following these tips, you can optimize your PCB layout for better performance and functionality.

Latest Developments:

- Advanced CPWG calculators now consider the height of copper traces for more accurate results.

- Using a 0.032-inch trace width on a standard PCB material offers excellent return loss at 6 GHz.

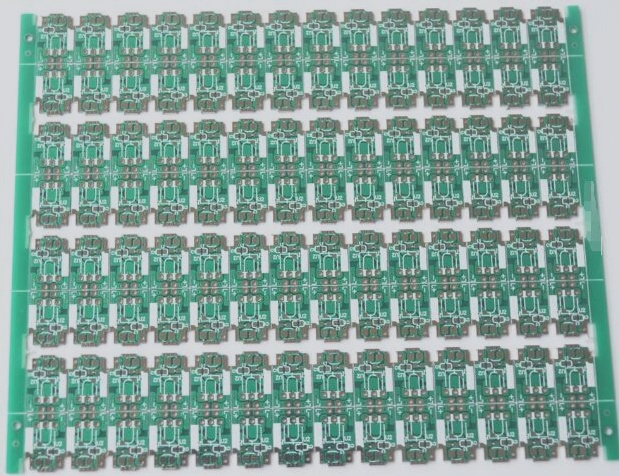

- 0603-sized SMT components and SMA edge-launch connectors are compatible with CPWG structures.

- Proper spacing adjustments accommodate larger SMT component pad dimensions.

Stay updated with the latest advancements in PCB design to enhance your RF circuit performance and reliability.

Best Practices for Interfacing with SMT Components

When interfacing with Surface Mount Technology (SMT) components or Integrated Circuits (IC) with pads narrower than 0.032 inches, it is crucial to limit the center conductor as close to the part as possible. This ensures a reliable connection and optimal performance.

It is important to note that if the suspension is physically small, its impact will be minimal, especially at lower frequencies. However, at very high frequencies, the size and design of the suspension become critical for maintaining signal integrity.

For optimal results when working with SMT components, pay close attention to the proximity of the center conductor to the part, especially when dealing with components with narrow pads.