1. The quality of a four-layer PCB circuit board is defined by IPC standards. The surface treatment includes anti-oxidation. If the vacuum packaging remains intact, the board can be stored for up to six months. Once unpacked, the board should be used within 24 hours in a controlled temperature and humidity environment. If stored unpacked, it should be used within one year. After unpacking, it must be assembled within a week under controlled temperature and humidity conditions. Gold boards follow stricter control processes compared to tin boards.

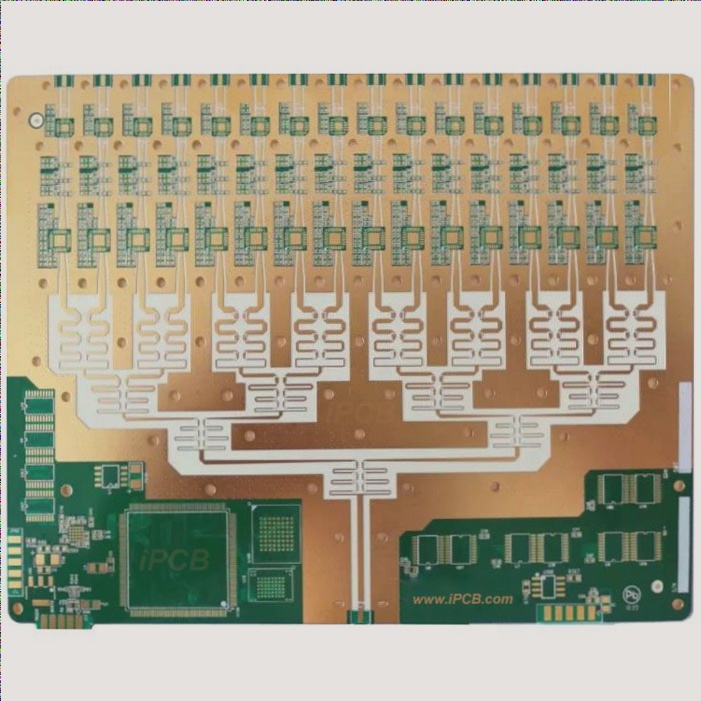

2. Generally, a four-layer circuit board consists of top and bottom layers for signal routing, with two middle layers. The middle layers typically include INTERNAL PLANE1 and INTERNAL PLANE2, designated using the DESIGN/LAYER STACK MANAGER command. These layers serve as power planes (e.g., VCC) and ground planes (e.g., GND), respectively, connecting corresponding net labels. Care should be taken not to use ADD LAYER, as this increases MIDPLAYER, primarily used for multi-layer PCB signal routing.

3. A four-layer PCB is composed of four layers of glass fiber. It is commonly used in applications like SDRAM to mitigate noise interference, despite increasing PCB costs.

The general principles of multi-layer PCB circuit board layout and routing

The general principles that PCB designers need to follow in the circuit board routing process are as follows:

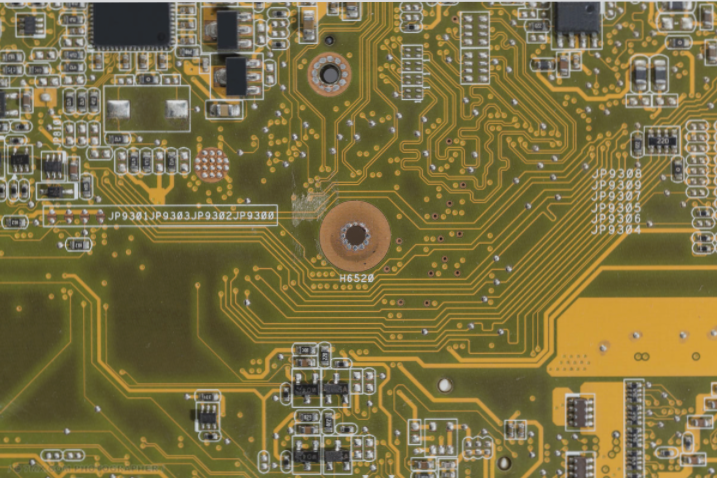

(1) The principle of setting the spacing of printed traces of components. The spacing constraint between different networks is based on electrical insulation, manufacturing process limitations, and component size. For instance, if the pin pitch of a chip component is 8mil, the clearance constraint cannot exceed 10mil. PCB designers must establish a specific 6mil design rule for the chip. Additionally, spacing considerations should account for manufacturer production capabilities.

Electrical insulation is crucial when dealing with significant potential differences between components or networks. In a typical environment, the safe gap for voltage is 200V/mm, equivalent to 5.08V/mil. Therefore, circuits with both high and low voltages on the same board require ample safety clearance to prevent interference.

(2) The choice of line cornering. To facilitate manufacturing and enhance aesthetic appeal, careful attention is needed when setting the corner style and wiring form. Options include 45°, 90°, and arc transitions. Sharp corners should generally be avoided; arc or 45° transitions are preferable to 90° or sharper angles.

Smooth transitions between wires and pads are essential to prevent sharp protrusions; teardropping can resolve this issue. When the distance between pads is less than the pad diameter D, the trace width can match the pad diameter. If the distance exceeds D, the trace width should not exceed the pad diameter. When a trace passes between pads without connecting to them, it should maintain an equal and maximum distance from each pad.

(3) Determining trace width. Trace width is determined by factors such as current levels and interference resistance. Higher currents necessitate wider traces, with power lines wider than signal lines. Ground lines should also be robust to maintain ground potential stability. For instance, with a 0.05mm thick copper film, a 1mm wide trace can handle 20A/mm². Signal lines typically require widths of 10-30 mils, while high current lines require 40 mils or more, with line-to-line spacing exceeding 30 mils to ensure reliability and impedance control.

For power and ground lines, if space permits on the PCB, wider traces should be used to enhance waveform stability, ideally exceeding 50 mils.

(4) Anti-interference and electromagnetic shielding of PCB traces. Interference sources include crosstalk between signal lines and noise from power lines. Effective layout and grounding strategies can mitigate these issues, improving the electromagnetic compatibility of the PCB design.

These principles guide PCB designers in achieving robust, interference-resistant layouts, crucial for reliable circuit performance and manufacturing efficiency.