Advancements in High-Speed PCB Interconnect Design Technology

High-speed PCB board interconnect design technology involves testing, simulation, and adherence to specific standards. The accuracy of interconnection design analysis is crucial for successful implementation. Traditional signal waveform testing requires attention to probe lead length to avoid noise interference.

New Trends in Interconnect Test Technology

In recent years, with the continuous increase in signal rates, the landscape of testing has transformed significantly. Beyond oscilloscopes, engineers now focus on addressing power supply ground noise, synchronous switching noise (SSN), and jitter. RF instruments are being integrated into interconnect design testing.

- Calibration methods for testing

- Modeling techniques for passive devices

- Power integrity testing

- Clock signal jitter testing methods

Calibration Methods for Network Analyzers

Network analyzers require rigorous calibration, unlike spectrum analyzers and oscilloscopes. Common calibration methods include Thru, TRL, and SOLT. Thru calibration normalizes test results and is suitable for scenarios where high accuracy is not essential. TRL calibration is beneficial for non-coaxial structures like PCB boards, allowing flexibility in calibration port extension. SOLT calibration, a standard method, involves 12 calibration error parameters, ensuring accurate calibration in coaxial structures.

Testing Passive Devices

When testing passive devices, spectrum analyzers offer a straightforward calibration process using internal standard sources. Oscilloscope calibration is even simpler, requiring connection to an internal standard source for quick verification.

The Importance of Passive Devices in Signal Chain

- Connectors play a crucial role in high-speed signal integrity designs.

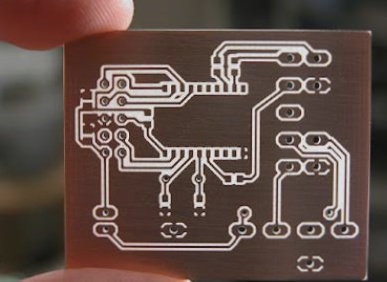

- PCB board traces and vias are essential for signal transmission.

- Capacitors and inductors (magnetic beads) are commonly used passive components.

In high-speed signal integrity designs, connectors have a significant impact on signal links. Calibration fixtures are often created using the TRL calibration method to test and model connectors for simulation analysis. The testing and modeling methods for PCB traces and vias are similar to those of connectors, utilizing TRL calibration to position the test port accurately.

Capacitance Modeling for Signal and Power Integrity

Capacitance models are crucial for signal integrity and power integrity analyses. Impedance analyzers and network analyzers are commonly used for capacitance modeling in different frequency bands. Impedance analyzers are suitable for low-frequency bands, while network analyzers are ideal for high-frequency bands. When using a network analyzer for power integrity testing, it’s essential to cover the entire frequency band for accurate modeling.

Inductors (magnetic beads) are often utilized in traditional power supply designs to reduce noise interference. To prevent resonance issues, it’s essential to model and simulate inductors accurately. The modeling method for inductors is similar to capacitance modeling but in series mode, unlike the parallel mode used for capacitors.

The modeling of passive devices is crucial for signal integrity and power integrity. In recent years, the simulation analysis of Electromagnetic Interference (EMI) has gained importance, leading to a focus on testing and modeling EMI passive devices in interconnect design.

Power Integrity Testing: Power supply impedance characteristic table of a single board.

Recent Developments:

EMI simulation analysis is on the rise, emphasizing the testing and modeling of EMI passive devices in interconnect design.

Power Integrity Testing in PCB Design

With the advancement in chip technology leading to increased power and decreased operating voltage, power supply noise has become a critical consideration in interconnection design. Power integrity testing involves two main steps: power system characteristic testing and power ground noise testing.

Power System Characteristic Testing

- Utilizes a network analyzer to test Self-Impedance and Transfer-Impedance of the power system.

- Impedance of the power system is obtained using the formula S21=Z/50.

Power Ground Noise Testing

- Uses a spectrum analyzer and oscilloscope to test ground noise of the power supply.

- DC-Blocking must be used in the test fixture to prevent DC component interference.

Synchronous Switching Noise Test

For testing power supply ground noise in chips, a synchronous switching noise test is crucial. This test involves toggling N-1 IO ports simultaneously while keeping one static to analyze the signal waveform for synchronous switching noise.

Jitter Testing in High-End Products

Jitter has become a significant factor affecting product performance in high-end products. Using a spectrum analyzer to test clock signal jitter can help troubleshoot issues effectively.

Testing Clock Signal Jitter

- Clock signals are typically generated by crystal oscillators or phase-locked loops.

- Use a spectrum analyzer to analyze clock signal spectrum for side lobes indicating jitter.

- Test power supply noise of crystal oscillators or phase-locked loops to identify the cause of clock jitter.

Solution

Redesign the filter circuit of crystal oscillators or phase-locked loops based on the clock spectrum side lobes to mitigate clock jitter issues, often by optimizing filter capacitor selection.

Interconnect Design Testing: Current Trends and Future Directions

- Introduction to the Latest Test Objects and Methods

- Emerging Test Content:

- Power-to-ground noise analysis

- Passive device modeling

- Jitter measurements

- Proposed Test Methodology

- Optimizing Signal Waveform Tests

- Future Focus: Chip Packaging and Beyond

As signal frequencies rise, new challenges in interconnect design testing are emerging. To address these challenges, the author suggests a novel approach based on practical experience.

When conducting traditional signal waveform tests, it is crucial to minimize ground wire length to prevent noise interference and ensure accurate results.

With increasing signal frequencies, the future of interconnect design will center around chip packaging. This shift will drive advancements in testing and modeling techniques for PCB boards.