Utilizing IBIS Models for Signal Integrity Analysis in PCB Design

When working on a printed circuit board (PCB) project, leveraging a digital input/output buffer information specification (IBIS) simulation model can provide valuable insights for signal integrity analysis and guide design decisions. Extracting key variables from the IBIS model is crucial for a successful PCB design process.

Understanding Signal Integrity Challenges

When digital signals travel along transmission lines on a PCB, they exhibit wave-like behavior rather than simple voltage changes, especially over long distances. Impedance matching plays a vital role in preventing signal reflections, similar to waves in a pool interacting with different impedances. Impedance mismatches can lead to significant signal integrity issues.

Addressing Impedance Mismatches

Designers can reduce signal reflections by matching PCB trace resistances at the signal ends. Understanding the impedance characteristics of integrated circuits (ICs) and PCB traces acting as transmission lines is essential for addressing system resistance and impedance matching issues.

- Modeling each connection unit as a distributed transmission line helps in simulating the PCB transmission path effectively.

- Key IC pin specifications, such as transmitter output resistance, rise and fall times, receiver input resistance, and pin capacitance, can be derived from the IC’s IBIS model during PCB design.

- Defining transmission lines with parameters like characteristic impedance, propagation delay, track propagation delay, and track length is crucial for accurate simulation.

Calculating Line Propagation Delay

The line propagation delay for a specific PCB design can be calculated using the formula:

tD = D × LENGTH

For example, for an FR-4 board, a linear trace may have a propagation delay of 178 ps/inch with a characteristic impedance of 50 ohms.

Validating Results

Measuring the inductance and capacitance of traces on the PCB and inserting these values into appropriate formulas helps validate the results. Parameters like trace capacitance, trace inductance, and dielectric constants play a crucial role in determining the characteristic impedance and propagation delay of the transmission line.

By understanding and utilizing the IBIS model effectively, designers can enhance signal integrity analysis and make informed decisions during PCB design.

Comparison of Aggregate Circuits and Distributed Circuits

- Aggregated systems are typically small in size, while distributed circuits occupy more board space.

- Aggregated systems have a small effective length and signal speed slower than the fastest electrical characteristic.

Qualifying as an Aggregated System

- To qualify as an aggregated system, the circuit on the PCB must meet specific requirements, including the rise time (tRise).

IBIS Model Data Structure

- The IBIS model’s data structure is based on the power supply voltage range of the IC.

- IBIS models include corner data points determined by silicon process, power supply voltage, and junction temperature.

Transmitter Specifications and Signal Integrity

- Transmitter parameters for signal integrity evaluation include output impedance (ZT), rise time (tRise), and fall time (tFall).

- Figure 5 displays the IBIS model files for the TI ADS1296 package.

Input and Output Pin Impedance

- The impedance of any signal pin is a combination of model impedance, package inductance, and capacitance.

- Specific pin inductance and capacitance values are crucial for signal integrity.

Using IBIS for Transmission Line Design

- IBIS models can help identify and solve transmission line issues in PCB designs.

- Utilizing IBIS models is essential for optimizing transmission line performance.

Termination Strategy and Waveform Correction

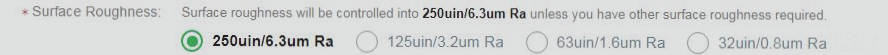

- Examining the IBIS model for input/output impedance, rise time, and capacitance is crucial for PCB transmission line design.

- Simulation using IBIS models helps in identifying key product specifications and correcting waveform issues.