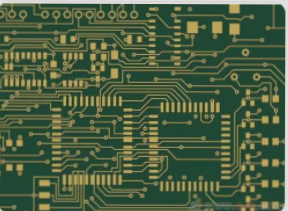

– **Mechanical Layer**: Defines the physical dimensions and overall structure of the PCB. It dictates the shape and size of the board.

– **Keepout Layer (Prohibited Wiring Layer)**: Specifies areas on the copper side where routing is not allowed. Once the keepout layer is defined, no traces or components with electrical characteristics can extend beyond this boundary during the layout process.

– **Top Overlay (Top Silkscreen Layer) & Bottom Overlay (Bottom Silkscreen Layer)**: Define the silkscreen markings on the top and bottom sides of the PCB, typically including component designators and other relevant text or symbols.

– **Top Paste (Top Solder Paste Layer) & Bottom Paste (Bottom Solder Paste Layer)**: Represent the areas where solder paste is applied for component mounting, usually corresponding to the copper pads exposed to the surface.

– **Top Solder Mask & Bottom Solder Mask**: These layers cover the copper traces, except for the areas where pads or vias are located. They are typically applied with a green solder mask to protect the copper and prevent solder bridges.

– **Drill Guide Layer**: Provides guidance for drilling holes for vias or through-hole components. It helps in defining the placement of the holes in the manufacturing process.

– **Drill Drawing Layer**: Shows the locations and sizes of all drilled holes, including via holes and mounting holes.

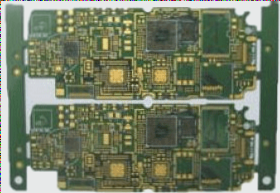

– **Multilayer**: Refers to the collective set of layers within the PCB design, encompassing all of the above layers and any additional internal layers (for multi-layered PCBs).

2. **How to set the layers of a 4-layer board with PowerPCB?**

In PowerPCB, the layer definitions for a 4-layer board can be set as follows:

1. No plane + Component (Top Route)

2. CAM Plane or Split/Mixed (Ground)

3. CAM Plane or Split/Mixed (Power)

4. No Plane + Component (For single-sided components, this can be defined as No Plane + Route)

**Notice**: Be mindful of the specific design requirements and layer stackup configuration for optimal signal integrity and power distribution.

1. The power and ground layers generated by the CAM plane are negative and cannot be routed on this layer. In contrast, the split/mixed layer generates a positive film, which can be used as either a power supply or ground, or it can be routed on this layer. However, it is recommended to route on the power and ground layers, as doing so on this layer could compromise its integrity and potentially lead to EMI issues. To define the layer, add the power network (such as 3.3V, 5V, etc.) from the list on the left to the list on the right in Layer 2’s assignment.

2. “Conduct signal integrity analysis, establish corresponding routing rules, and route according to these rules.” What is your understanding of this sentence?

Pre-simulation analysis helps generate a range of layout and routing strategies to ensure signal integrity. These strategies are typically converted into physical design rules that constrain PCB layout and routing. Common rules include topology, length, impedance, parallel spacing, and parallel length constraints. PCB tools can then complete routing based on these constraints, though the final results must be verified through post-simulation analysis.

3. For a 4-layer PCB, with the middle two layers being VCC and GND, and routing going from top to bottom, what is the return path from the bottom layer to the top layer? Is it through a VIA or power?

The return path of a signal through a VIA is not explicitly defined, but it is generally assumed that the return signal will flow through the nearest ground or power-connected VIA. In simulation, EDA tools often treat vias as an RLC network with fixed lumped parameters, which is a worst-case estimate.

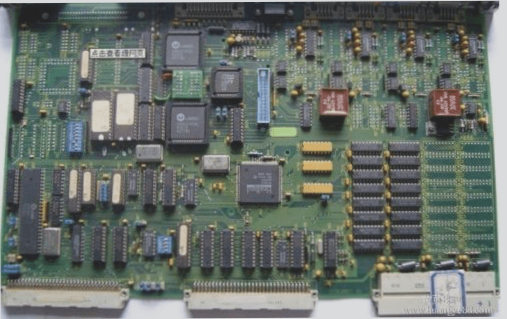

4. When using PROTEL to create a schematic, the netlist generated for board production is always incorrect, preventing automatic PCB generation. What could be the cause?

You may need to manually edit the generated netlist according to the schematic, then perform an automated routing after passing the checks. Automatic layout and routing with board-making software often do not produce ideal results. The netlist error could be caused by missing component packages in the schematic or the layout library, or by mismatches between them. For single-sided boards, it is not recommended to use automatic routing; however, for double-sided boards, it can be used. It is best to route power and important signal lines manually, while leaving other signals for automatic routing.

5. How should you select PCB software?

Choose PCB software based on your specific needs. There are many advanced options available, but the key is to find software that matches your design capabilities, scale, and constraints. A tool that is fast and easy to use may seem appealing, but be careful as it could lead to inefficiencies or mistakes. Consider meeting with an EDA vendor for a product demonstration. Even if you don’t make a purchase, the discussion can provide valuable insights.

6. How do you draw and bind ICs in PROTEL?

In PROTEL, use the mechanical layer to create the bonding diagram for the PCB. The IC’s substrate pin connections to VCC, GND, or float should be defined according to the IC’s specifications. The mechanical layer can then be used to print the bonding diagram.

7. How should you understand the concepts of broken copper and floating copper?

From a PCB manufacturing perspective, copper areas smaller than a certain threshold are typically called broken copper. These small copper areas can cause problems during the etching process due to errors. Electrically, floating copper refers to copper that is not connected to any DC network. Floating copper can act like an antenna, picking up interference from surrounding signals. Floating copper may be small broken pieces or large copper areas.

8. Is there a relationship between near-end and far-end crosstalk with signal frequency and signal rise time? Will they change as these factors change? Can a formula explain their relationship?

Yes, the crosstalk from the offending network to the victim network is influenced by the signal edge rate. The faster the edge transition, the greater the crosstalk (V = L * di/dt). The impact of crosstalk on the victim network also depends on the signal frequency. Higher frequencies tend to result in stronger crosstalk.

9. The connection between PCBs is typically made using gold-plated or silver “fingers.” What if the contact between the “fingers” and the socket is poor?

If the issue is cleaning, use a specialized electrical contact cleaner or even an eraser to clean the PCB surface. Other potential causes include: 1. The gold finger may be too thin, or the pad may not match the socket; 2. The socket may contain contaminants or impurities; 3. The quality of the socket itself may be subpar.

If you have any PCB manufacturing needs, please do not hesitate to contact me.Contact me