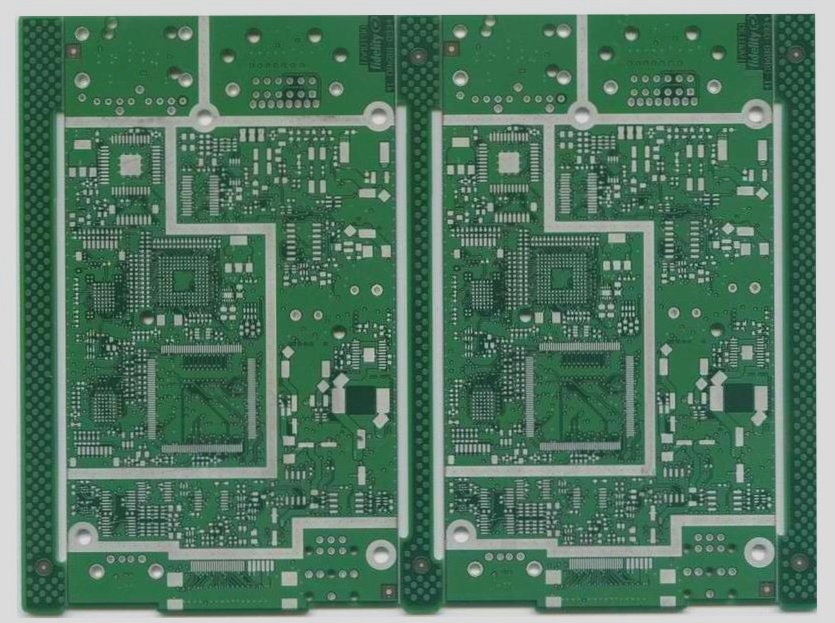

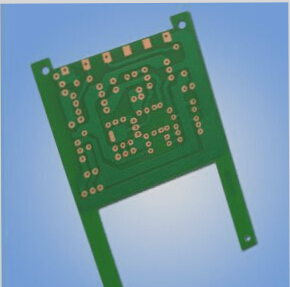

Ultra-Low-Cost Hybrid Tuner for Single-Layer PCB Board Design

When it comes to designing a hybrid tuner for TV and video converter box applications, the focus is on achieving low cost, low power consumption, small size, and selecting the right external components. The latest single-chip ULC tuner is a game-changer. This tuner integrates RF and IF circuits, operates at lower power consumption, and uses a single-layer PCB board, reducing system costs significantly.

Key Features:

- Supports both analog and digital TV signals

- Handles mixed signals like DVB-T/PAL/SECAM, ISDB-T/NTSC, and ATSC/NTSC

- Integrates RF tuner and IF module

- Utilizes a simple triplex circuit for frequency band switching

- Employs pre-stage tracking notch filter and image frequency compensation circuit for signal quality

TUA6039-2 Tri-Band Tuner IC:

The TUA6039-2 is a complete tri-band tuner IC that includes 3 mixers, 3 oscillators, 1 SAW driver, and 1 IF amplifier. It offers excellent phase noise performance, making it suitable for all digital devices. With low power consumption and wideband AGC detector, this tuner is ideal for portable devices.

Advantages of Single-Layer PCB Design:

- Cost-effective solution

- Handles various TV standards efficiently

- Significant power savings for portable devices

In conclusion, the single-layer PCB tuner design excels in performance and cost-effectiveness, making it a preferred choice for customers in the competitive TV tuner market. The design’s ability to handle multiple TV standards while maintaining low power consumption sets it apart in the industry.

Challenges in Developing PCB Reference Design for ULC Tuner

Developing the reference design for the ULC tuner poses several challenges, particularly in placing the chip’s VQFN package on the PCB. Grounding on a single-layer PCB can limit flexibility, which is crucial in RF design. Grounding plays a critical role in tuner design, affecting key electrical parameters such as spurious signal rejection from the crystal, PLL reference frequency, and the integrated DC/DC converter in the ULC tuner.

Electrical Parameter Impact

- DC-DC Frequency Spurious Rejection: Achieves about 52dB

- VCO Reference Frequency Spurious Rejection: Achieves about 60dB

Another issue arising from the VQFN package and single-layer PCB is heat dissipation of the IC. To address this, the reference design exposes the backside of the IC to enhance thermal performance, particularly through the tuner’s frame. Operating at 3.3V not only reduces power consumption but also minimizes heat generation.

Market Demands and Design Balance

The increasing demand for RF tuner electronics in multimedia applications is pushing manufacturers to prioritize form factor, power efficiency, and cost reduction. The ULC tuner design aims to strike a balance between cost, performance, and power consumption. Utilizing the TUA6039-2 component enables a high-performance hybrid tuner with an energy-efficient 3.3V supply voltage. Employing a single-layer PCB further cuts costs.

In conclusion, the ULC tuner reference design mitigates product design risks, accelerates time to market, and maintains performance and quality standards on the PCB board.