Understanding PCB Trace Width Variations and Impedance Effects

- When designing PCBs, trace width variations can impact impedance and signal quality.

- Impedance changes should be kept below 10% to avoid signal reflection issues.

- Factors to consider include impedance change extent, signal rise time, and delay introduced by narrow lines.

Dealing with Impedance Changes in PCB Design

When the PCB impedance changes, it’s crucial to assess the potential impact on signal quality. For instance, a sudden change from 8 mils to 6 mils in line width can lead to reflections exceeding the noise budget requirement of 5% of the voltage swing. This can be mitigated through impedance matching termination techniques.

Managing Multiple Impedance Changes

In cases where the PCB impedance changes twice, careful consideration of the timing and length of the narrow trace is essential. By ensuring that reflections from impedance changes cancel each other out, signal integrity can be maintained. Research suggests that as long as the time delay at the impedance change is less than 20% of the signal rise time, issues can be avoided.

Key Considerations in PCB Trace Design

Designers must analyze impedance changes, signal rise times, and the length of narrow trace sections to anticipate potential signal integrity issues. Minimizing the length of narrow traces can help reduce impedance-related reflections.

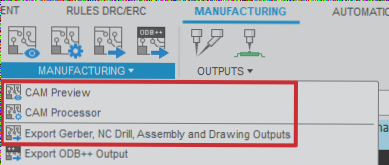

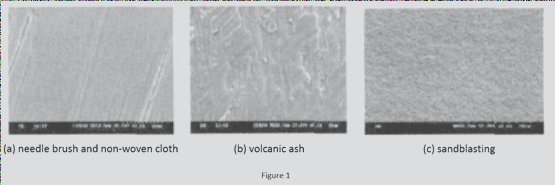

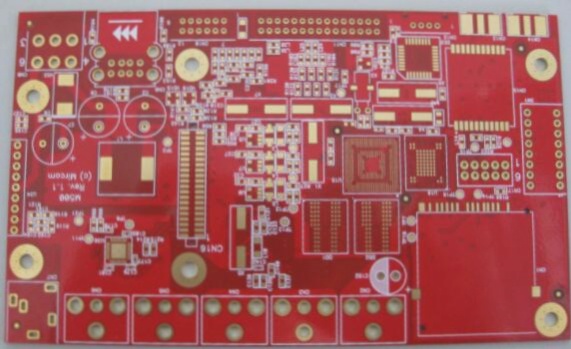

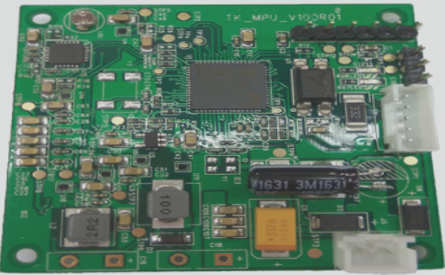

Practical Application in PCB Manufacturing

While theoretical calculations provide guidance, practical PCB manufacturing may require adjustments based on real-world conditions. It’s advisable to start with conservative estimates and refine designs based on actual manufacturing outcomes to balance performance and cost considerations.

Looking for PCB Manufacturing Services?

Don’t hesitate to reach out if you have any PCB manufacturing needs. Our team at Well Circuits is here to help you with all your PCB requirements.

Feel free to contact us for more information or to get started on your project today.