1. **How to Choose EDA Tools?**

In current PCB design software, thermal analysis is not a strong feature, so it is not recommended to rely on it. For other functions such as 1.3.4, you can opt for PADS or Cadence, as they offer good cost performance. For beginners in PLD design, it is advisable to use the integrated environment provided by PLD chip manufacturers. For designs involving more than one million gates, single-point tools can be used effectively.

2. **Recommended EDA Software for High-Speed Signal Processing and Transmission**

For conventional circuit design, INNOVEDA’s PADS is an excellent choice, as it comes with matching simulation software. This type of design typically accounts for 70% of applications. However, for high-speed circuit design or analog-digital hybrid circuits, Cadence provides a solution with superior performance and value. Of course, Mentor also offers solid performance, particularly with its design flow management, which is arguably one of the best in the industry. (Wang Sheng, Technical Expert at Datang Telecom)

3. **Explanation of the Meaning of Each Layer on a PCB**

– **Top Overlay**: This layer displays the names of components on the top side, also referred to as the top silkscreen or top component legend (e.g., R1, C5, IC10).

– **Bottom Overlay**: Similar to the top overlay, this refers to the component names on the bottom side of the PCB.

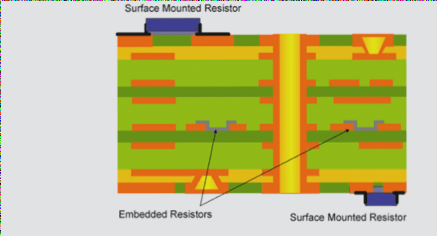

– **Multilayer**: If you’re designing a 4-layer PCB and place a free pad or via, defining it as a multilayer will ensure that its pad appears on all four layers. However, if you only define it as the top layer, the pad will appear only on the top layer.

4. **What aspects should be considered in high-frequency PCB design, routing, and layout above 2 GHz?**

High-frequency PCBs above 2 GHz fall under the design of RF circuits, which is distinct from high-speed digital circuit design. The layout and routing of RF circuits must be considered in conjunction with the schematic, as they will introduce parasitic effects that can impact performance. Additionally, some passive components in RF designs are realized using parameterized definitions and specially shaped copper traces. As a result, EDA tools must support parametric components and the ability to edit these custom copper shapes. Mentor’s BoardStation, for example, includes a specialized RF design module that can accommodate these needs. Furthermore, RF design often requires dedicated RF circuit analysis tools. Among the leading industry tools is Agilent’s EESof, which integrates well with Mentor’s design tools.

5. **What design guidelines should be followed for microstrip routing in high-frequency PCBs above 2 GHz?**

Designing RF microstrip lines requires the use of 3D field analysis tools to extract the transmission line parameters. All design rules should be specified and enforced within these field extraction tools to ensure proper signal integrity and performance.

6. **For a PCB with all digital signals, where an 80 MHz clock source is present, what kind of circuit should be used for protection in addition to grounding mesh to ensure sufficient drive capability?**

To ensure sufficient clock driving capability, the clock signal should not rely on protection circuits; instead, a dedicated clock driver chip is typically used. The primary concern for clock driving capability arises from multiple clock loads. The clock driver chip takes the single clock signal and distributes it to multiple loads via point-to-point connections. When selecting a clock driver, it is essential to match the driver to the load requirements, ensuring that the signal edges meet the necessary timing specifications (usually edge-triggered for clocks). The delay introduced by the clock driver should also be accounted for in the overall system timing analysis.

7. **When using a separate clock signal board, what kind of interface should be used to minimize the impact on clock signal transmission?**

To minimize the effects of transmission line impedance, keeping the clock signal path as short as possible is crucial. Using a separate clock signal board typically increases the signal path length, which may introduce additional concerns regarding grounding and power distribution. For long-distance transmission, differential signaling is recommended. LVDS signals, for example, provide adequate drive capability, but for slower clock speeds, this may not be necessary.

8. **For a 27 MHz SDRAM clock line (80-90 MHz), where the second and third harmonics are in the VHF band and interference is significant, what other methods can be used to reduce this interference apart from shortening the trace length?**

If the third harmonic is pronounced and the second harmonic is minimal, this could indicate that the signal has a 50% duty cycle, which results in a lack of even harmonics. In such cases, adjusting the signal’s duty cycle may help mitigate the harmonic issues. Additionally, if it is a unidirectional clock signal, series termination at the source can be used to dampen secondary reflections without significantly impacting the clock edge rate. The optimal series termination value can be calculated using the following formula.

9. **In PCB layout and design, what is meant by the topological structure of a trace?**

Topology, also referred to as routing order, refers to the arrangement and connection sequence of traces in a PCB network, especially in multi-port connections. It is a critical factor that influences the signal path and overall layout efficiency.

10. **How can the routing topology be adjusted to improve signal integrity?**

Routing topology is a complex aspect of network design, as the impact on signal integrity can vary depending on whether the signals are unidirectional, bidirectional, or of different voltage levels. The influence of topology on signal quality is not straightforward, making it challenging to determine the best topology purely from a theoretical standpoint. Pre-simulation of different routing topologies requires a deep understanding of the circuit’s design principles, signal types, and the complexity of the routing process, placing significant demands on engineers.

If you have any PCB manufacturing needs, please do not hesitate to contact me.Contact me

In current PCB design software, thermal analysis is not a strong feature, so it is not recommended to rely on it. For other functions such as 1.3.4, you can opt for PADS or Cadence, as they offer good cost performance. For beginners in PLD design, it is advisable to use the integrated environment provided by PLD chip manufacturers. For designs involving more than one million gates, single-point tools can be used effectively.

2. **Recommended EDA Software for High-Speed Signal Processing and Transmission**

For conventional circuit design, INNOVEDA’s PADS is an excellent choice, as it comes with matching simulation software. This type of design typically accounts for 70% of applications. However, for high-speed circuit design or analog-digital hybrid circuits, Cadence provides a solution with superior performance and value. Of course, Mentor also offers solid performance, particularly with its design flow management, which is arguably one of the best in the industry. (Wang Sheng, Technical Expert at Datang Telecom)

3. **Explanation of the Meaning of Each Layer on a PCB**

– **Top Overlay**: This layer displays the names of components on the top side, also referred to as the top silkscreen or top component legend (e.g., R1, C5, IC10).

– **Bottom Overlay**: Similar to the top overlay, this refers to the component names on the bottom side of the PCB.

– **Multilayer**: If you’re designing a 4-layer PCB and place a free pad or via, defining it as a multilayer will ensure that its pad appears on all four layers. However, if you only define it as the top layer, the pad will appear only on the top layer.

4. **What aspects should be considered in high-frequency PCB design, routing, and layout above 2 GHz?**

High-frequency PCBs above 2 GHz fall under the design of RF circuits, which is distinct from high-speed digital circuit design. The layout and routing of RF circuits must be considered in conjunction with the schematic, as they will introduce parasitic effects that can impact performance. Additionally, some passive components in RF designs are realized using parameterized definitions and specially shaped copper traces. As a result, EDA tools must support parametric components and the ability to edit these custom copper shapes. Mentor’s BoardStation, for example, includes a specialized RF design module that can accommodate these needs. Furthermore, RF design often requires dedicated RF circuit analysis tools. Among the leading industry tools is Agilent’s EESof, which integrates well with Mentor’s design tools.

5. **What design guidelines should be followed for microstrip routing in high-frequency PCBs above 2 GHz?**

Designing RF microstrip lines requires the use of 3D field analysis tools to extract the transmission line parameters. All design rules should be specified and enforced within these field extraction tools to ensure proper signal integrity and performance.

6. **For a PCB with all digital signals, where an 80 MHz clock source is present, what kind of circuit should be used for protection in addition to grounding mesh to ensure sufficient drive capability?**

To ensure sufficient clock driving capability, the clock signal should not rely on protection circuits; instead, a dedicated clock driver chip is typically used. The primary concern for clock driving capability arises from multiple clock loads. The clock driver chip takes the single clock signal and distributes it to multiple loads via point-to-point connections. When selecting a clock driver, it is essential to match the driver to the load requirements, ensuring that the signal edges meet the necessary timing specifications (usually edge-triggered for clocks). The delay introduced by the clock driver should also be accounted for in the overall system timing analysis.

7. **When using a separate clock signal board, what kind of interface should be used to minimize the impact on clock signal transmission?**

To minimize the effects of transmission line impedance, keeping the clock signal path as short as possible is crucial. Using a separate clock signal board typically increases the signal path length, which may introduce additional concerns regarding grounding and power distribution. For long-distance transmission, differential signaling is recommended. LVDS signals, for example, provide adequate drive capability, but for slower clock speeds, this may not be necessary.

8. **For a 27 MHz SDRAM clock line (80-90 MHz), where the second and third harmonics are in the VHF band and interference is significant, what other methods can be used to reduce this interference apart from shortening the trace length?**

If the third harmonic is pronounced and the second harmonic is minimal, this could indicate that the signal has a 50% duty cycle, which results in a lack of even harmonics. In such cases, adjusting the signal’s duty cycle may help mitigate the harmonic issues. Additionally, if it is a unidirectional clock signal, series termination at the source can be used to dampen secondary reflections without significantly impacting the clock edge rate. The optimal series termination value can be calculated using the following formula.

9. **In PCB layout and design, what is meant by the topological structure of a trace?**

Topology, also referred to as routing order, refers to the arrangement and connection sequence of traces in a PCB network, especially in multi-port connections. It is a critical factor that influences the signal path and overall layout efficiency.

10. **How can the routing topology be adjusted to improve signal integrity?**

Routing topology is a complex aspect of network design, as the impact on signal integrity can vary depending on whether the signals are unidirectional, bidirectional, or of different voltage levels. The influence of topology on signal quality is not straightforward, making it challenging to determine the best topology purely from a theoretical standpoint. Pre-simulation of different routing topologies requires a deep understanding of the circuit’s design principles, signal types, and the complexity of the routing process, placing significant demands on engineers.

If you have any PCB manufacturing needs, please do not hesitate to contact me.Contact me