The Influence of Wiring Topology on Signal Integrity

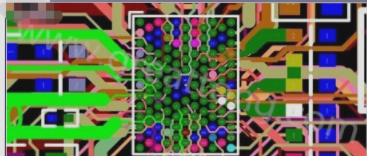

Signal integrity issues in high-speed PCB designs can be impacted by the wiring topology used. When signals travel along transmission lines on high-speed PCBs, the wiring topology plays a crucial role in maintaining signal quality. A star-shaped distribution from a central point to each device can help promote consistent signal transmission and reflection delays, enhancing overall signal quality. However, factors such as signal topology nodes, operating principles, and buffer configurations must be carefully considered when implementing a star topology to ensure optimal signal integrity.

The Impact of Pads on High-Speed Signals

When it comes to high-speed signals in PCB design, the influence of pads cannot be overlooked. Pads play a significant role in determining signal quality, especially as signals travel through various components such as bonding wires, pins, package shells, and solder joints. Each component along this pathway can affect signal integrity, making it essential to consider the impact of pads on high-speed signals. While traditional analyses may rely on package parameters in IBIS models, emerging trends are shifting towards utilizing V-I and V-T curves for buffer characterization and SPICE models for describing package parameters to ensure accurate simulations for high-frequency signals.

Strategies for Mitigating Electromagnetic Interference in PCB Design

- EMC/EMI in high-speed PCB design

- Impact of PCB design on electromagnetic compatibility

- Reducing product development cycle time

- Accelerating time to market

- Focus on EMC/EMI mitigation strategies

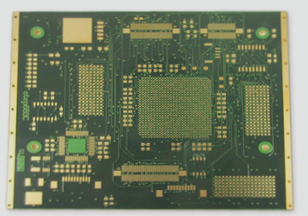

Suppressing electromagnetic interference (EMI) is crucial in PCB design, as PCBs can be significant sources of EMI. Prioritizing EMC/EMI in high-speed PCB design can significantly reduce the product development cycle and accelerate time to market. Engineers are focusing on strategies for mitigating electromagnetic interference. During EMC testing, serious harmonics of the clock signal were detected. Special measures may need to be taken for the power supply pins of the IC utilizing the clock signal. Currently, only decoupling capacitors are connected to these power supply pins. Considerations in PCB design to minimize electromagnetic radiation include examining how harmonics propagate, addressing the conduction mode of propagation with power supply decoupling, and implementing appropriate matching and shielding.

Effective Filtering for Mitigating EMC Radiation

- Filtering as a strategy for mitigating EMC radiation

- Consideration of interference sources and victims

- Use of oscilloscope to analyze signal characteristics

- Avoidance of signals with a 50% duty cycle

- Benefits of measures like land coverage for victims

Filtering is an effective strategy for mitigating EMC radiation through conduction. When addressing interference sources, using an oscilloscope to analyze signal characteristics is advisable. Issues such as signal edge speed, reflection, overshoot, undershoot, or ringing should be identified. Matching can be considered to address these problems. It is recommended to avoid creating signals with a 50% duty cycle, as they lack even sub-harmonics and contain more high-frequency components. For victims of electromagnetic interference, measures like land coverage may be beneficial.