In the process of converting circuit board designs and PCB layouts, differences in data or file formats across software platforms often necessitate the use of additional tools for conversion. This article will guide you through the conversion skills from Protel to Allegro.

1. Protel Schematic to Capture CIS

We can utilize the new features of Protel DXP SP2 to facilitate the conversion of Protel schematics directly into Capture CIS. Here, we present a few key considerations based on practical experience.

1) When Protel DXP generates the Capture DSN file, it does not include package information. Consequently, in Capture, the PCB Footprint attributes for all components will be empty. We need to manually input the packaging details, which is often the most time-consuming aspect of the entire conversion process. While adding this information, ensure package consistency with the Protel PCB design and adhere to Cadence’s naming conventions. For instance, a resistor’s package named AXIAL0.4 in Protel will be altered to AXIAL04 in the package library conversion since Cadence disallows the use of periods in package names. Similarly, a DB9 connector packaged as DB9RA/F in Protel will be modified to DB9RAF. Thus, when adding package details in Capture, it’s crucial to account for these naming adjustments.

2) During the conversion, some hidden pins or pin numbers of devices may be lost and must be added in Capture through library editing. Discrete components like resistors and capacitors are typically the ones most prone to missing pin numbers.

3) In PCB hierarchical design, the bus connecting the modules must be named in Capture. Even if this bus has been named in the parent design within Protel, it needs to be recreated in Capture to ensure proper connection.

4) For a device with multiple parts in a package, it’s essential to modify its bit number. For instance, with a 74LS00, if you use two of the gates in Protel, they will be labeled U8A and U8B. This information will be lost during conversion and must be added again.

Overall, pay attention to the above points. With Protel DXP, we can convert Protel schematics into Capture, facilitating the conversion of the existing Protel schematic symbol library to Capture.

**Second, the conversion of the Protel package library**

Having used Protel for PCB design over time, we often accumulate a substantial Protel package library that has been validated through practical use. When switching design platforms, retaining this package library can be challenging. We will utilize Orcad Layout along with the free Cadence tool Layout2Allegro to accomplish this task.

1) Place a PCB package in an empty PCB within Protel, then output the PCB file in Protel PCB 2.8 ASCII format.

2) Import this Protel PCB 2.8 ASCII file into Orcad Layout.

3) Use Layout2Allegro to convert the generated Layout MAX files into Allegro BRD files.

4) Finally, employ Allegro’s Export function to output the package library and pad library, thus completing the conversion of the Protel package library to Allegro.

**Third, the conversion of Protel PCB to Allegro**

Building on the previous steps, we can now convert Protel PCB to Allegro. This process is essentially a design reproduction. We will replicate the Protel PCB layout and routing in Allegro.

1) Pass the Allegro format netlist generated in the second step from Capture to the Allegro BRD as the starting point for our reproduction efforts.

2) First, we need to replicate the device layout. Output the Place & Pick file in Protel, which contains complete information on device positions, rotation angles, and placement layers. This file can be manually adjusted into Allegro’s Placement file. By importing this Placement file into Allegro, we can achieve the layout.

3) To restore the wiring information, Specctra should be utilized as a bridge. First, export the Specctra DSN file containing wiring information from Protel. Keep the following two points in mind regarding this DSN file:

4) The layer names in Protel differ from those in Allegro. Use a text editor to make the necessary adjustments. For example, the top and bottom layers in Protel are referred to as Toplayer and Bottomlayer, whereas in Allegro, these layers are called TOP and BOTTOM.

5) Verify the definition of vias in Specctra and incorporate them into Allegro’s rules. Define vias in Allegro to output wiring information from Specctra. You can utilize sessiON, wires, and route files; it is advisable to use route files, then import the wiring information to reproduce the Allegro PCB layout, completing the conversion from Protel PCB to Allegro BRD.

**Protel to Allegro conversion method**

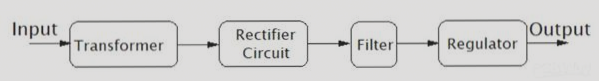

With the rapid advancement of today’s IT industry, the demands for hardware are increasing. PCB designers are challenged with the task of creating high-speed and high-density PCBs. As the saying goes, to do a good job, one must first sharpen their tools. This is why more PCB designers are moving away from low-end design tools in favor of high-performance EDA software from companies like Cadence.

However, such a transition often brings various challenges. Given the widespread use of Protel among users in China, those opting for Cadence’s high-speed PCB solutions face the task of migrating their Protel designs into Cadence PCB design software.

The challenges encountered in this migration can be categorized into two main types: the first involves simpler designs where the PCB designer wants to leverage Cadence CCT’s powerful automatic routing capabilities; the second involves complex designs where the designer relies on noise analysis tools for simulating signals and noise, and setting up the wiring topology.

For the first case, the conversion process is relatively straightforward. One can utilize the Protel to CCT conversion tool provided by either Protel or Cadence. In the second case, the process is more intricate, which we will briefly outline below.

The analysis target for Cadence’s signal-to-noise analysis tool is the BRD file of Cadence Allegro. Allegro is capable of reading third-party netlists that comply with its requirements. The Telexis format netlists generated by Protel meet these specifications, allowing Protel files to be injected into Allegro.

Two points for readers to consider: first, Allegro third-party netlists do not permit periods in the $PACKAGE section; second, in Protel, we use the format BasName[0:N] to represent a bus, and BasName[x] to denote a signal within the bus. In the Allegro third-party netlist, a signal within the bus is represented as BasNameX. Readers can resolve these issues by directly editing the Telexis netlist output by Protel.

Allegro also requires a device description file (Device.txt) for each type of device when injecting the third-party netlist. The format is as follows:

– Package: package type

– Class: classtype

– Pincount: total pinnumber

– Pinused: …

The commonly used fields are PACKAGE, CLASS, and PINCOUNT. PACKAGE describes the device’s package, but Allegro will utilize the PACKAGE item in the netlist while disregarding it in the device description file during netlist injection. CLASS categorizes the device for signal-to-noise analysis; Cadence classifies devices into IC, IO, and DISCRETE. PINCOUNT indicates the total number of pins on the device. For most devices, including these three fields in the Device.txt file suffices.

With third-party netlists and device description files, we can integrate the schematic design from Protel into Cadence PCB design software via netlist format. Subsequently, PCB designers can employ Cadence PCB software to develop high-speed and high-density PCBs, effectively leveraging its robust design capabilities.

If PCB layout work has already been performed in Protel, Allegro’s scripting function can replicate this layout within Allegro. In Protel, PCB designers can generate a Place & Pick file containing the position, rotation angle, and information of each device on the PCB’s top or bottom. From this file, an Allegro script can be easily created. By executing this script in Allegro, the layout from Protel can be reproduced. Below is the C++ code used to convert the Place & Pick file to an Allegro Script file. The author employed this code to reproduce a PCB layout with over 800 devices in Allegro in just a few minutes.

1. Protel Schematic to Capture CIS

We can utilize the new features of Protel DXP SP2 to facilitate the conversion of Protel schematics directly into Capture CIS. Here, we present a few key considerations based on practical experience.

1) When Protel DXP generates the Capture DSN file, it does not include package information. Consequently, in Capture, the PCB Footprint attributes for all components will be empty. We need to manually input the packaging details, which is often the most time-consuming aspect of the entire conversion process. While adding this information, ensure package consistency with the Protel PCB design and adhere to Cadence’s naming conventions. For instance, a resistor’s package named AXIAL0.4 in Protel will be altered to AXIAL04 in the package library conversion since Cadence disallows the use of periods in package names. Similarly, a DB9 connector packaged as DB9RA/F in Protel will be modified to DB9RAF. Thus, when adding package details in Capture, it’s crucial to account for these naming adjustments.

2) During the conversion, some hidden pins or pin numbers of devices may be lost and must be added in Capture through library editing. Discrete components like resistors and capacitors are typically the ones most prone to missing pin numbers.

3) In PCB hierarchical design, the bus connecting the modules must be named in Capture. Even if this bus has been named in the parent design within Protel, it needs to be recreated in Capture to ensure proper connection.

4) For a device with multiple parts in a package, it’s essential to modify its bit number. For instance, with a 74LS00, if you use two of the gates in Protel, they will be labeled U8A and U8B. This information will be lost during conversion and must be added again.

Overall, pay attention to the above points. With Protel DXP, we can convert Protel schematics into Capture, facilitating the conversion of the existing Protel schematic symbol library to Capture.

**Second, the conversion of the Protel package library**

Having used Protel for PCB design over time, we often accumulate a substantial Protel package library that has been validated through practical use. When switching design platforms, retaining this package library can be challenging. We will utilize Orcad Layout along with the free Cadence tool Layout2Allegro to accomplish this task.

1) Place a PCB package in an empty PCB within Protel, then output the PCB file in Protel PCB 2.8 ASCII format.

2) Import this Protel PCB 2.8 ASCII file into Orcad Layout.

3) Use Layout2Allegro to convert the generated Layout MAX files into Allegro BRD files.

4) Finally, employ Allegro’s Export function to output the package library and pad library, thus completing the conversion of the Protel package library to Allegro.

**Third, the conversion of Protel PCB to Allegro**

Building on the previous steps, we can now convert Protel PCB to Allegro. This process is essentially a design reproduction. We will replicate the Protel PCB layout and routing in Allegro.

1) Pass the Allegro format netlist generated in the second step from Capture to the Allegro BRD as the starting point for our reproduction efforts.

2) First, we need to replicate the device layout. Output the Place & Pick file in Protel, which contains complete information on device positions, rotation angles, and placement layers. This file can be manually adjusted into Allegro’s Placement file. By importing this Placement file into Allegro, we can achieve the layout.

3) To restore the wiring information, Specctra should be utilized as a bridge. First, export the Specctra DSN file containing wiring information from Protel. Keep the following two points in mind regarding this DSN file:

4) The layer names in Protel differ from those in Allegro. Use a text editor to make the necessary adjustments. For example, the top and bottom layers in Protel are referred to as Toplayer and Bottomlayer, whereas in Allegro, these layers are called TOP and BOTTOM.

5) Verify the definition of vias in Specctra and incorporate them into Allegro’s rules. Define vias in Allegro to output wiring information from Specctra. You can utilize sessiON, wires, and route files; it is advisable to use route files, then import the wiring information to reproduce the Allegro PCB layout, completing the conversion from Protel PCB to Allegro BRD.

**Protel to Allegro conversion method**

With the rapid advancement of today’s IT industry, the demands for hardware are increasing. PCB designers are challenged with the task of creating high-speed and high-density PCBs. As the saying goes, to do a good job, one must first sharpen their tools. This is why more PCB designers are moving away from low-end design tools in favor of high-performance EDA software from companies like Cadence.

However, such a transition often brings various challenges. Given the widespread use of Protel among users in China, those opting for Cadence’s high-speed PCB solutions face the task of migrating their Protel designs into Cadence PCB design software.

The challenges encountered in this migration can be categorized into two main types: the first involves simpler designs where the PCB designer wants to leverage Cadence CCT’s powerful automatic routing capabilities; the second involves complex designs where the designer relies on noise analysis tools for simulating signals and noise, and setting up the wiring topology.

For the first case, the conversion process is relatively straightforward. One can utilize the Protel to CCT conversion tool provided by either Protel or Cadence. In the second case, the process is more intricate, which we will briefly outline below.

The analysis target for Cadence’s signal-to-noise analysis tool is the BRD file of Cadence Allegro. Allegro is capable of reading third-party netlists that comply with its requirements. The Telexis format netlists generated by Protel meet these specifications, allowing Protel files to be injected into Allegro.

Two points for readers to consider: first, Allegro third-party netlists do not permit periods in the $PACKAGE section; second, in Protel, we use the format BasName[0:N] to represent a bus, and BasName[x] to denote a signal within the bus. In the Allegro third-party netlist, a signal within the bus is represented as BasNameX. Readers can resolve these issues by directly editing the Telexis netlist output by Protel.

Allegro also requires a device description file (Device.txt) for each type of device when injecting the third-party netlist. The format is as follows:

– Package: package type

– Class: classtype

– Pincount: total pinnumber

– Pinused: …

The commonly used fields are PACKAGE, CLASS, and PINCOUNT. PACKAGE describes the device’s package, but Allegro will utilize the PACKAGE item in the netlist while disregarding it in the device description file during netlist injection. CLASS categorizes the device for signal-to-noise analysis; Cadence classifies devices into IC, IO, and DISCRETE. PINCOUNT indicates the total number of pins on the device. For most devices, including these three fields in the Device.txt file suffices.

With third-party netlists and device description files, we can integrate the schematic design from Protel into Cadence PCB design software via netlist format. Subsequently, PCB designers can employ Cadence PCB software to develop high-speed and high-density PCBs, effectively leveraging its robust design capabilities.

If PCB layout work has already been performed in Protel, Allegro’s scripting function can replicate this layout within Allegro. In Protel, PCB designers can generate a Place & Pick file containing the position, rotation angle, and information of each device on the PCB’s top or bottom. From this file, an Allegro script can be easily created. By executing this script in Allegro, the layout from Protel can be reproduced. Below is the C++ code used to convert the Place & Pick file to an Allegro Script file. The author employed this code to reproduce a PCB layout with over 800 devices in Allegro in just a few minutes.